DIGILENT社のARTY S7基板でSpartan7を使用してみました

この記事の内容は以下の通りです。

Vivadoの使用方法や書き込みケーブルの使用方法を解説します。

Vivadoのインストール

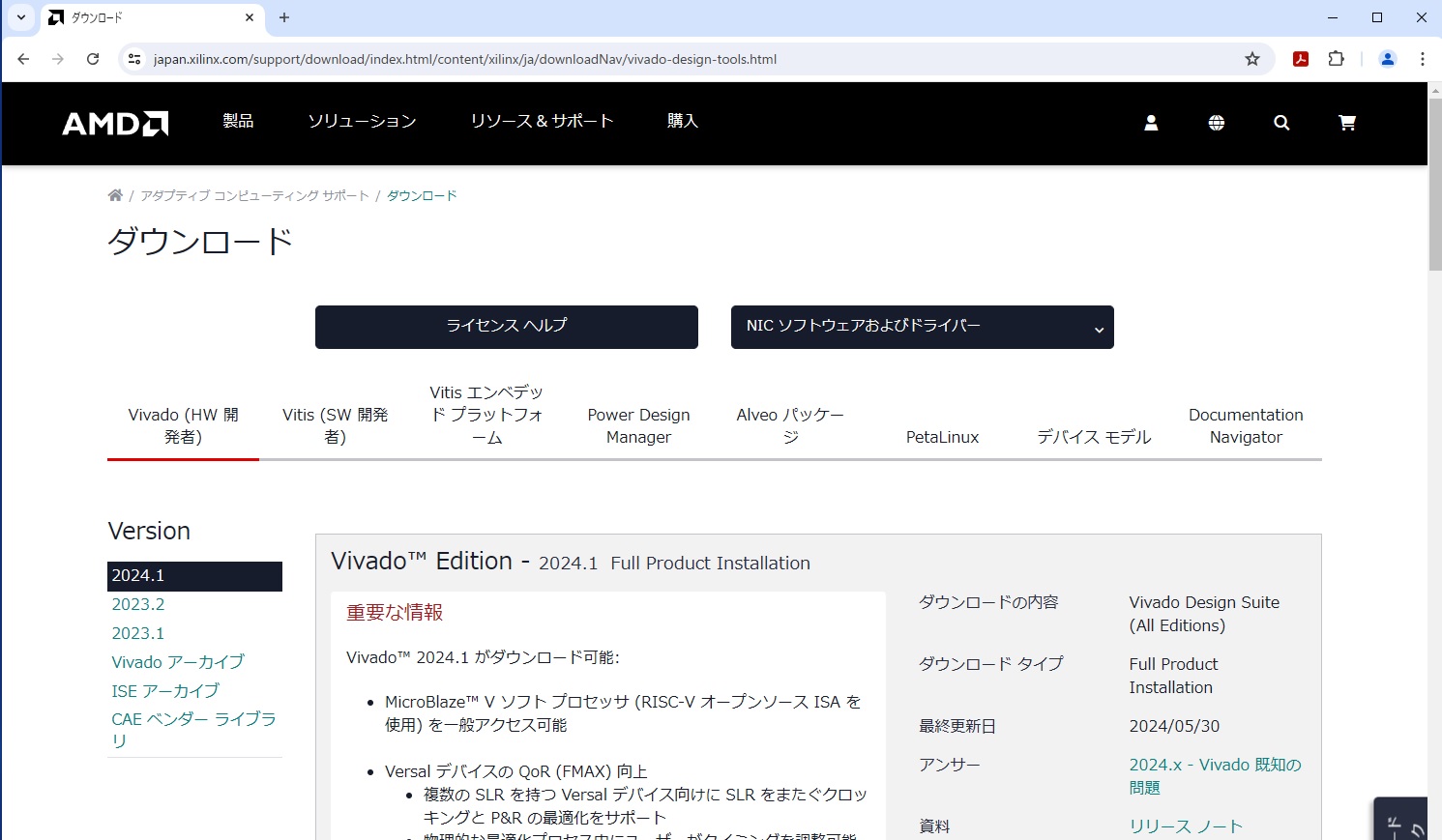

1.AMDのホームページからWebインストーラをダウンロード

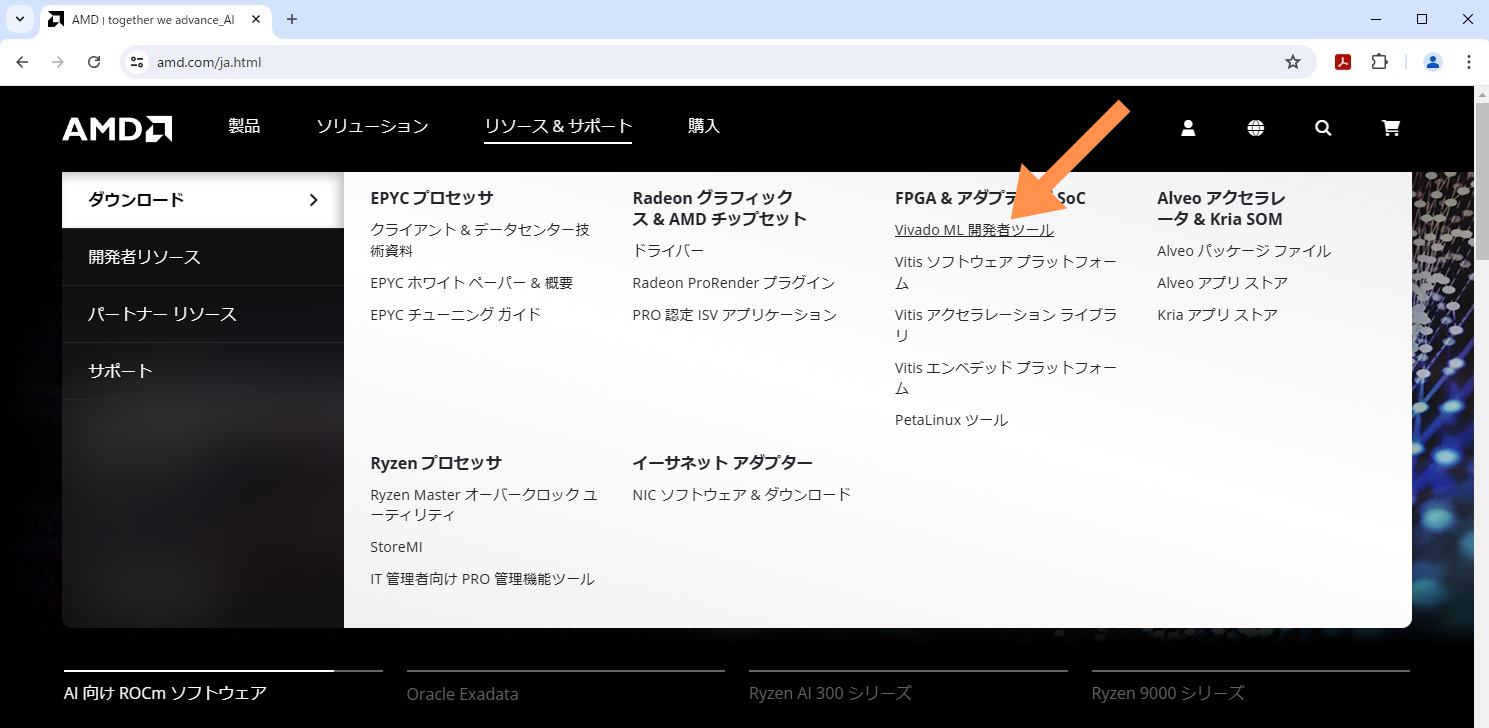

AMDのトップページです。

リソース&サポートをクリックします。

Vivado ML 開発者ツールをクリックします。

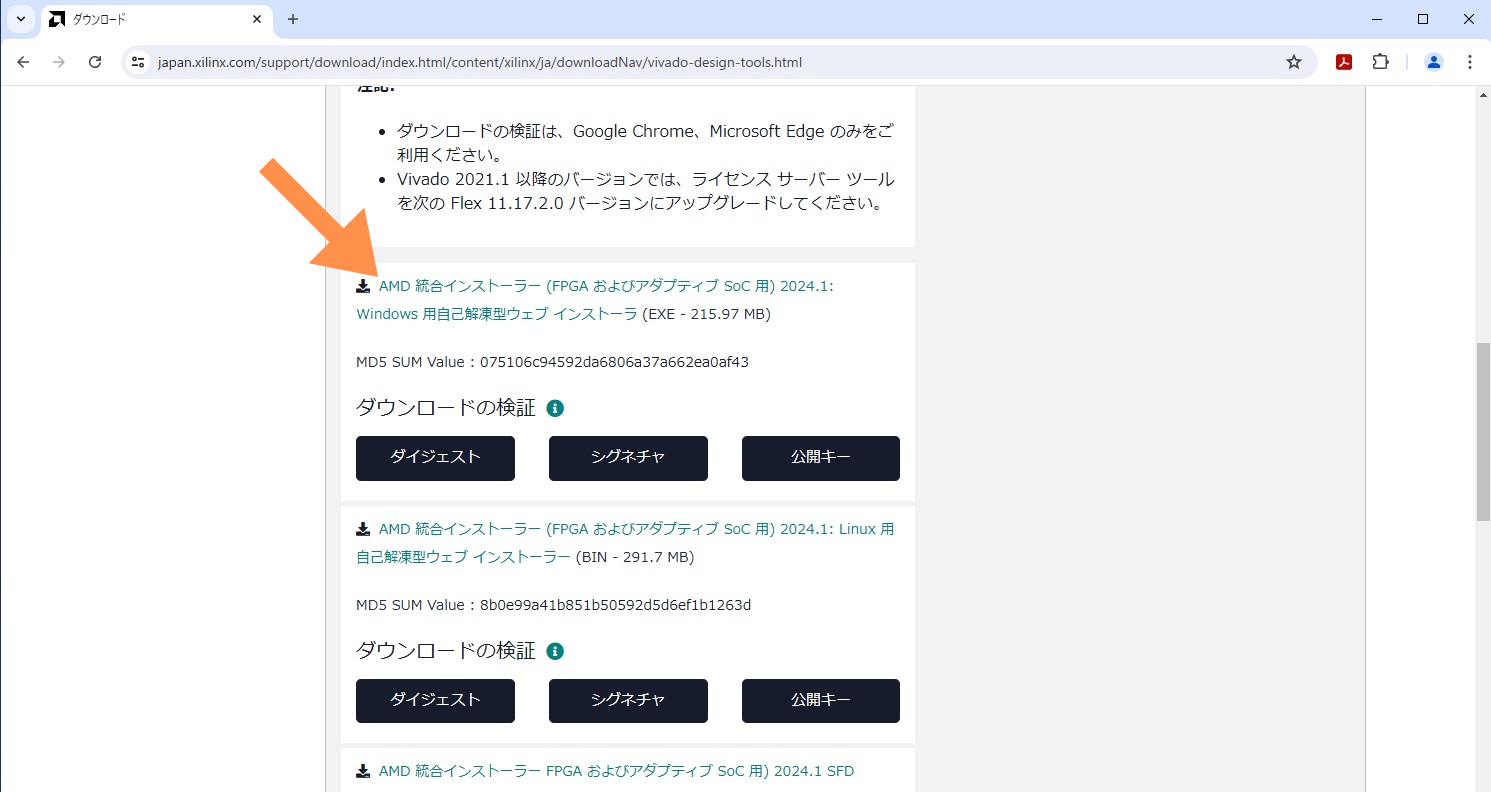

以下の画面が開くので、下へスクロールします。

Windows用Webインストーラをクリックしてダウンロードします。

2.アカウントの作成

インストーラをクリックするとアカウントの入力を要求されます。

アカウントを作成してある場合は「サインイン」をクリックします。

名前と住所の確認画面が表示されますので、確認して「Download」

ボタンを押します。

アカウントを作成していない場合は、サインイン画面で「アカウン

トの作成」をクリックしてアカウントを作成します。

3.ダウンロードしたWebインストーラを実行

下記ダウンロードファイルをダブルクリック

インストールが完了するとデスクトップに6つのアイコンが作成されます。

Vivadoを実行するときはVivado 2024.1をダブルクリックします。

![]()

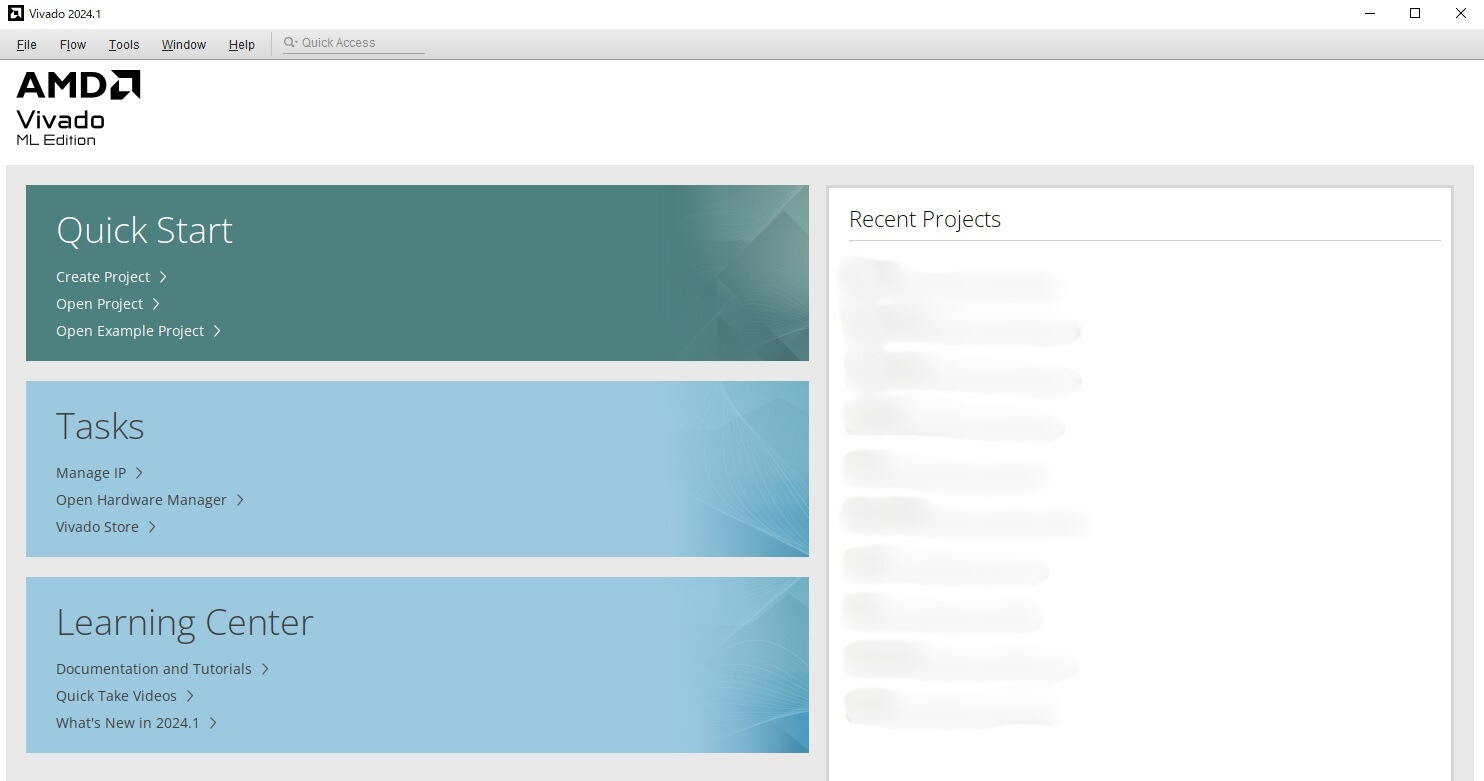

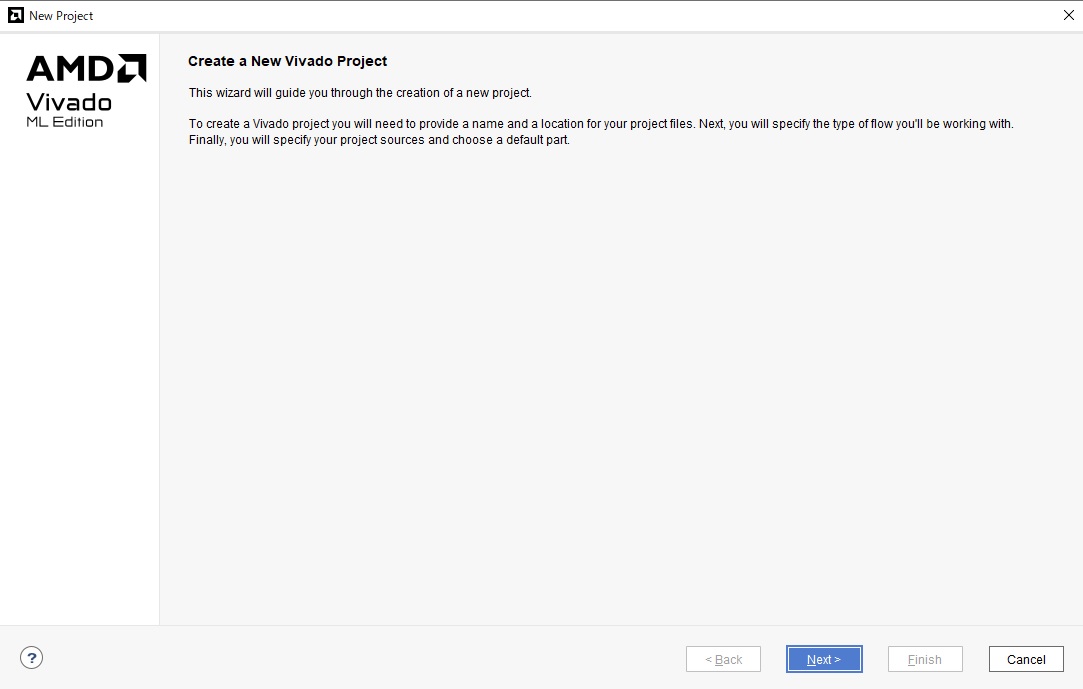

Vivadoの実行

Vivado 2024.1をダブルクリックすると初期画面が開きます。

最初はRecent Projectsは空です。

1. プロジェクトを作成します。

Quick StartのCreate Projectをクリック

Nextをクリック

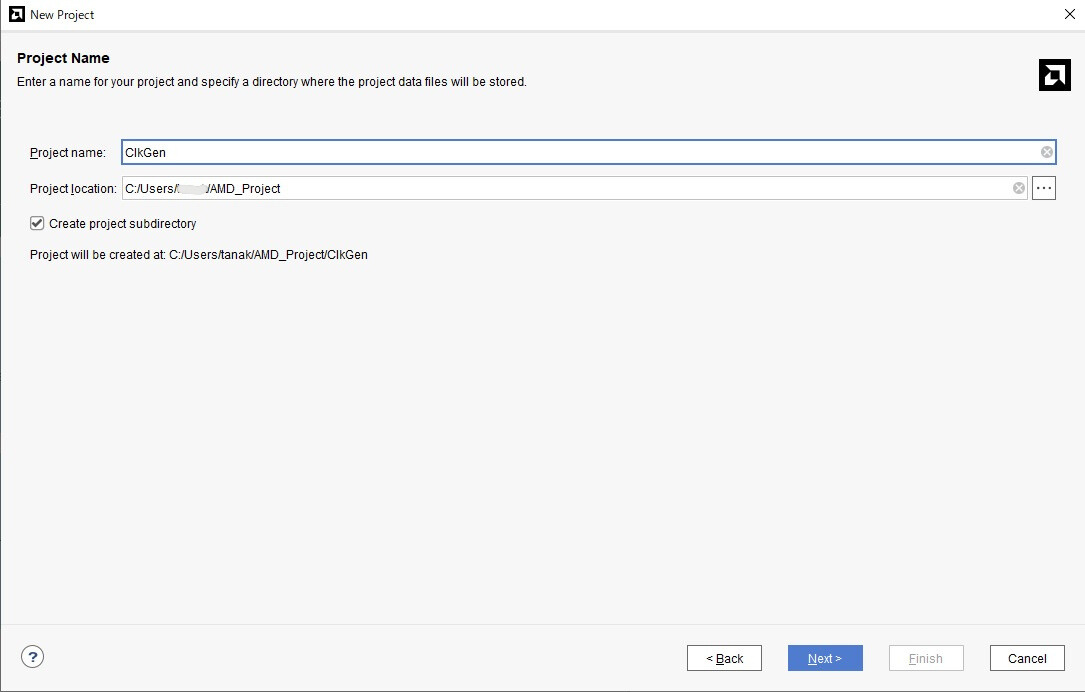

プロジェクト名を入力

Nextをクリック

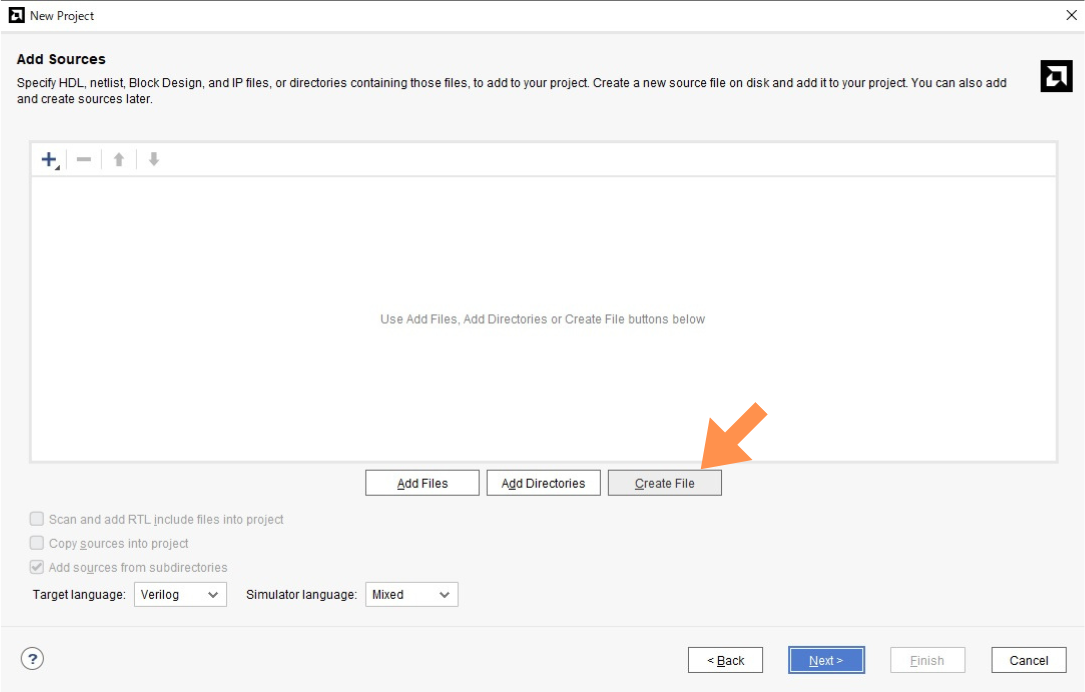

Nextをクリック

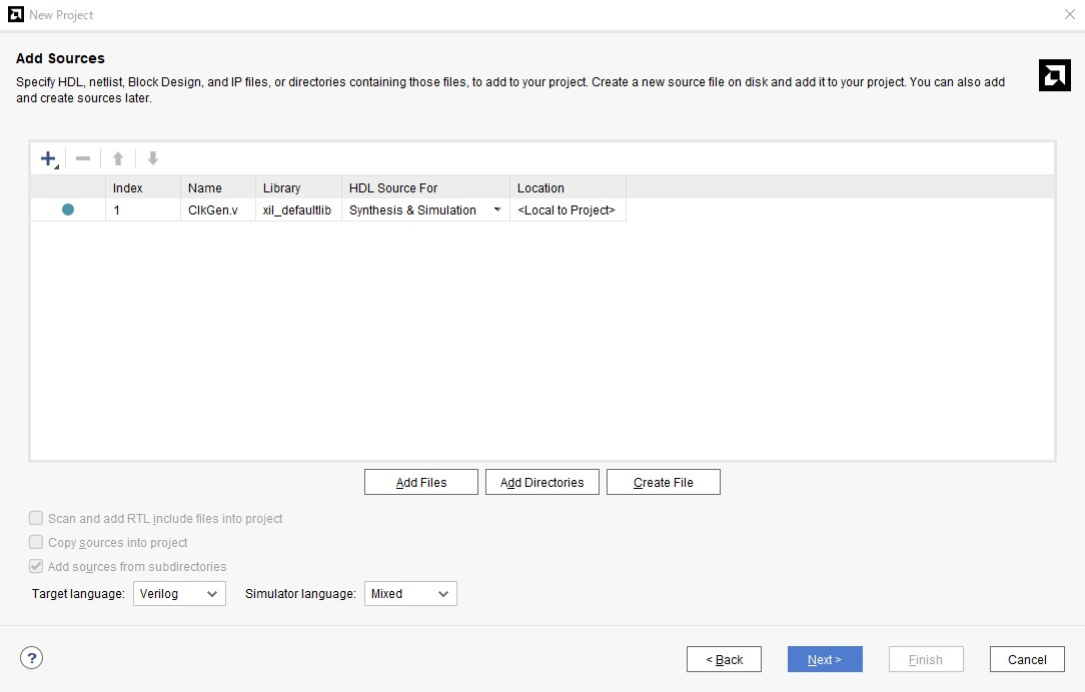

CreateFileをクリック

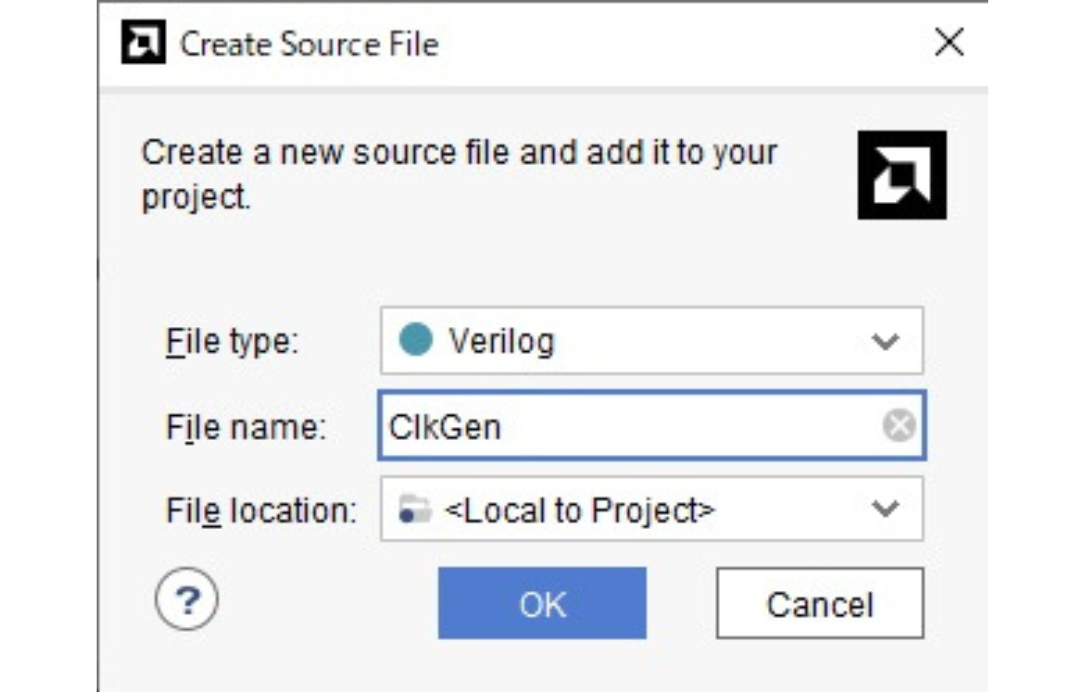

OKをクリック

ソースファイルが作成されましたので、Nextをクリック

中身は後で作成

2. 制約ファイルの作成(XDCファイル)

FPGAのピン配置を決めるため(制約するため)XDCファイルを作成します。

このファイルに、信号名とピン番号を記載することでピン配置を固定できます。

自身で作成した基板であればXDCファイルを作成する必要がありますが、

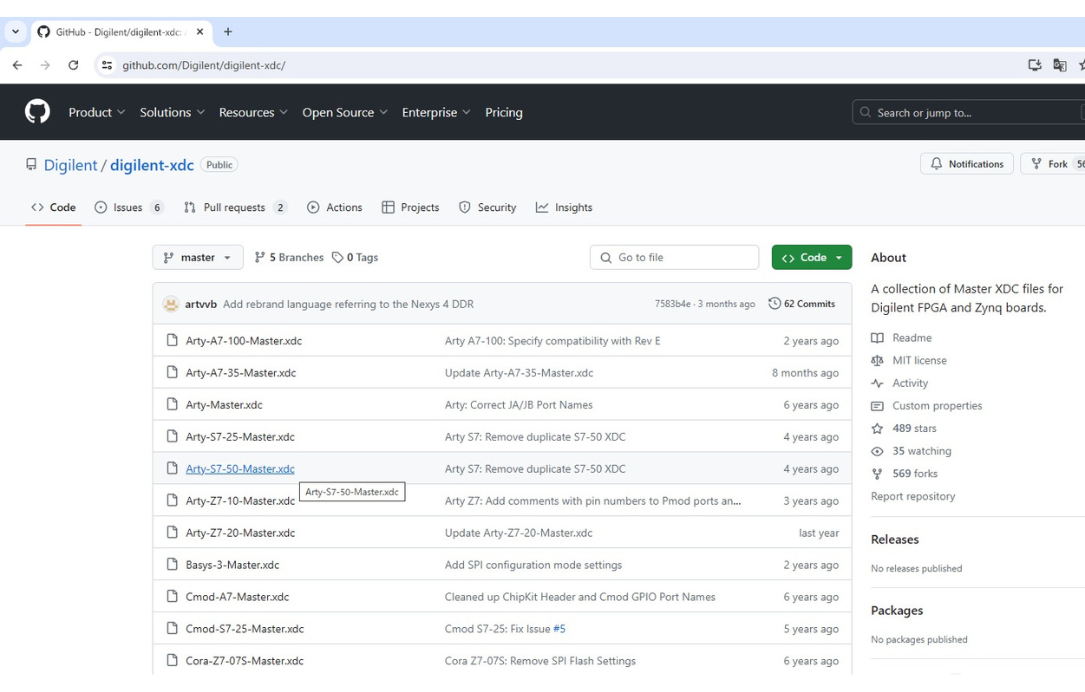

ArtyS7はメーカーが作成したXDCファイルをダウンロードして使用することができます。

下記からダウンロードして保存します。(Arty-S7-50-Master.xdc)

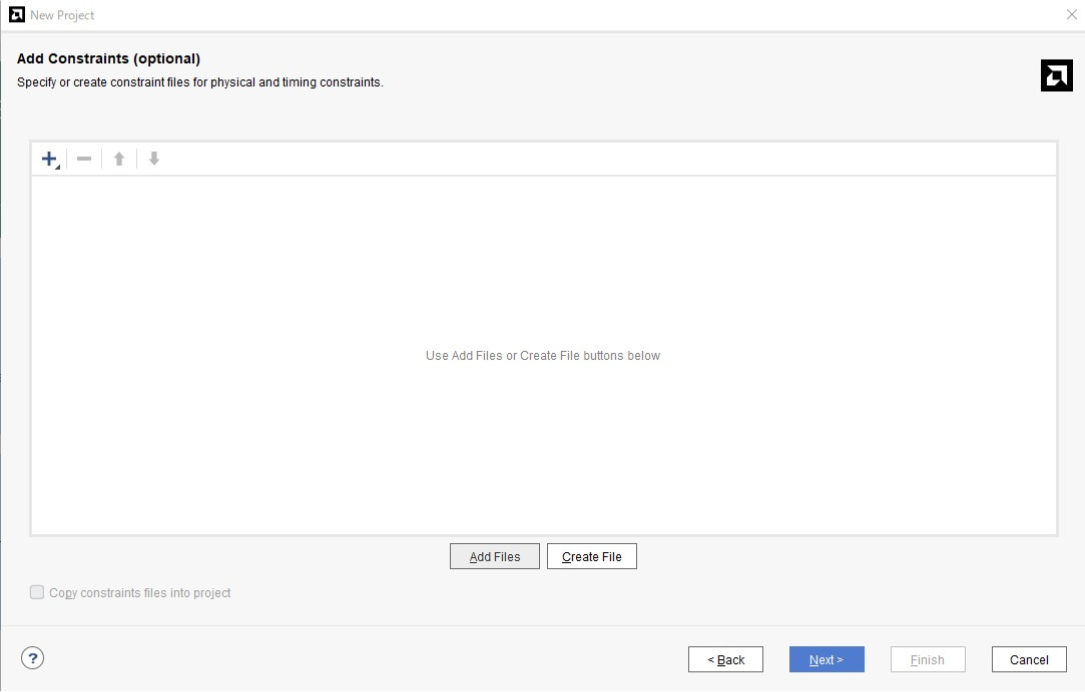

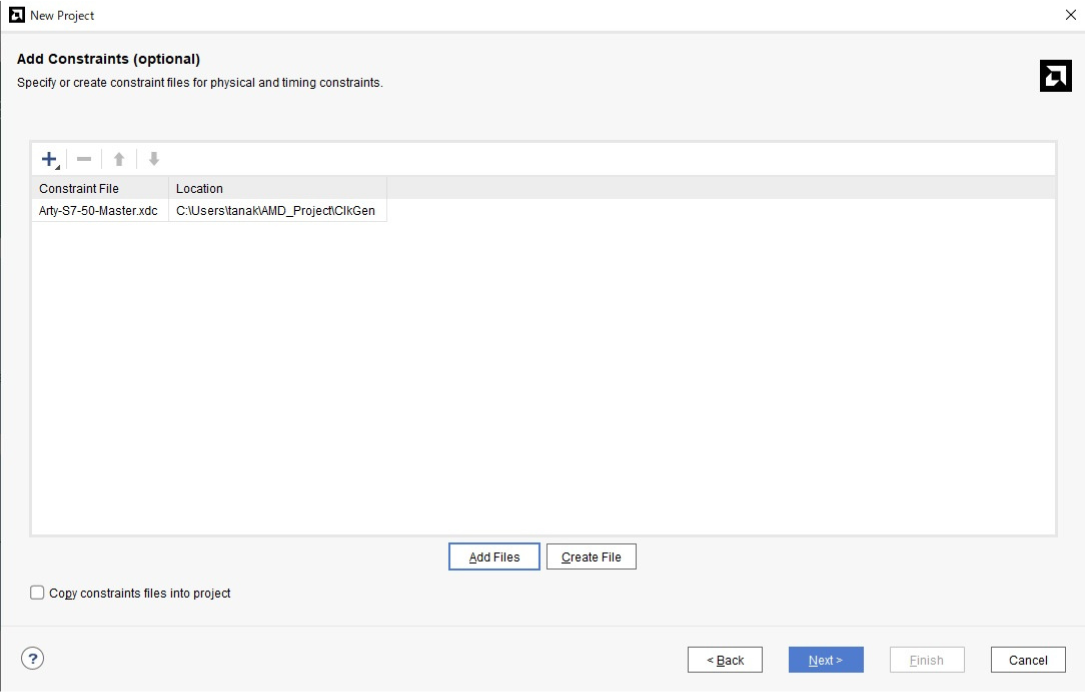

ソースファイルを作成してNextをクリックすると以下の画面が表示されますので、

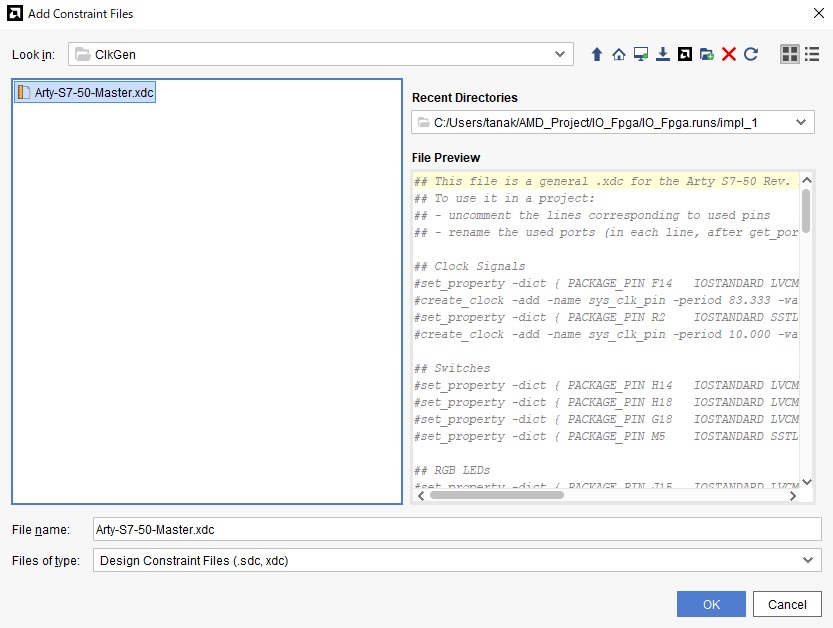

AddFilesをクリックして、ダウンロードしたXDCファイルを指定します。

ファイルを指定してOKをクリックします。

以下の通りProjectにXDCファイルが追加されました。

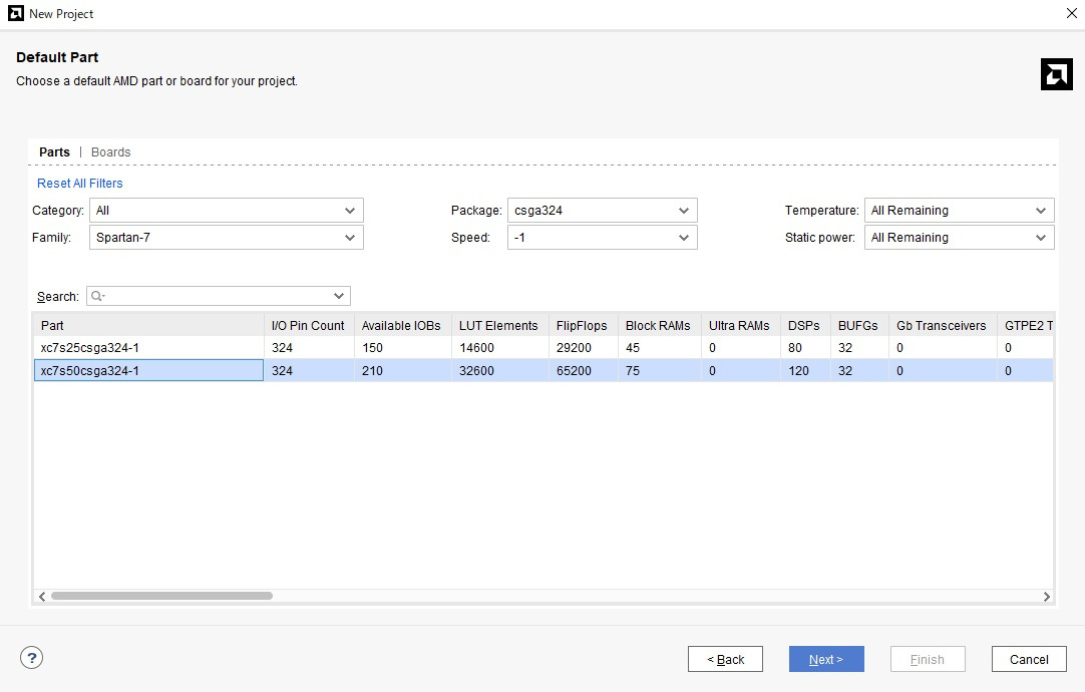

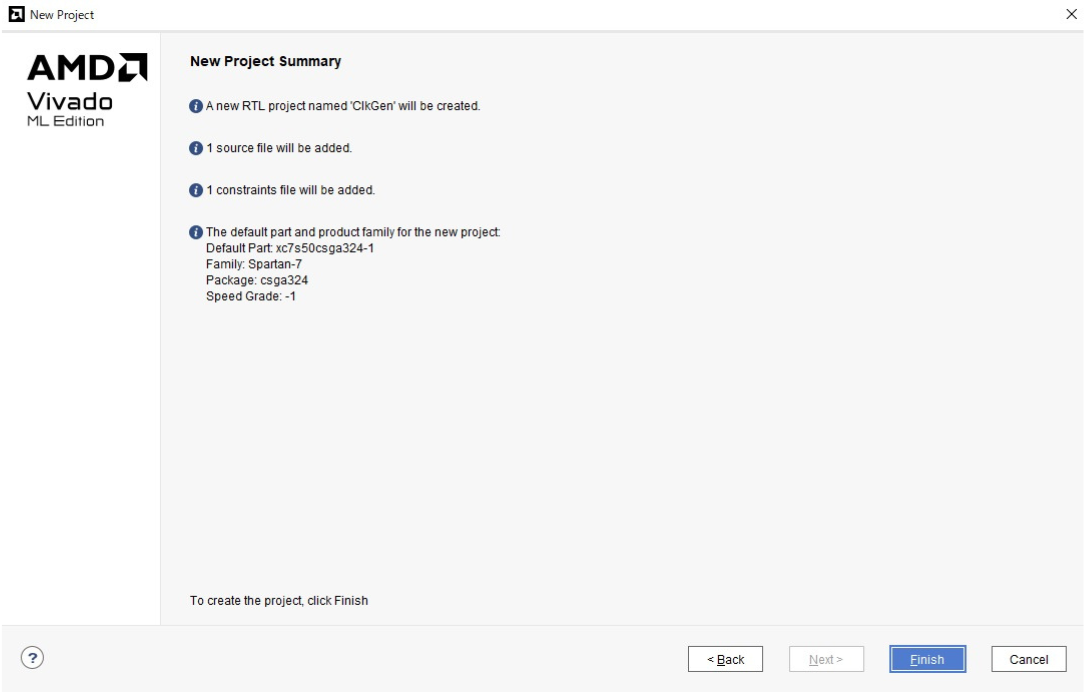

Nextをクリックし、次の画面でデバイスを指定します。

xc7s50csga324-1を選択してNextをクリックします。

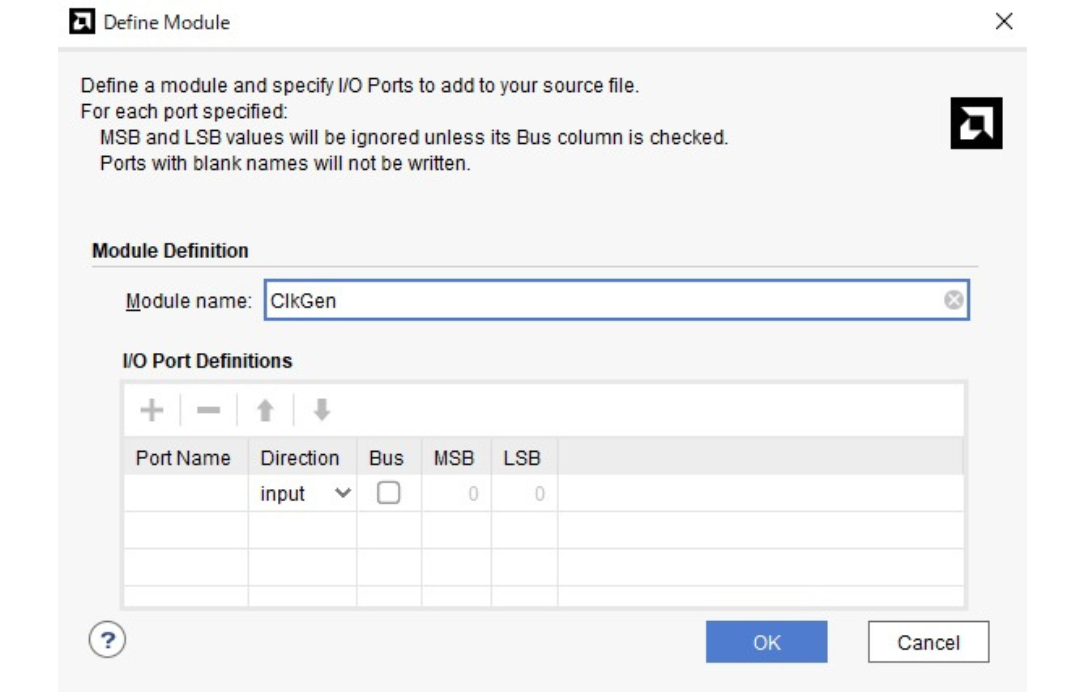

Define Module画面が表示され、ClkGenモジュールの入出力の定義を入力するように

促されますが、ここはこのままOKをクリックし、ソースファイルで記述するようにします。

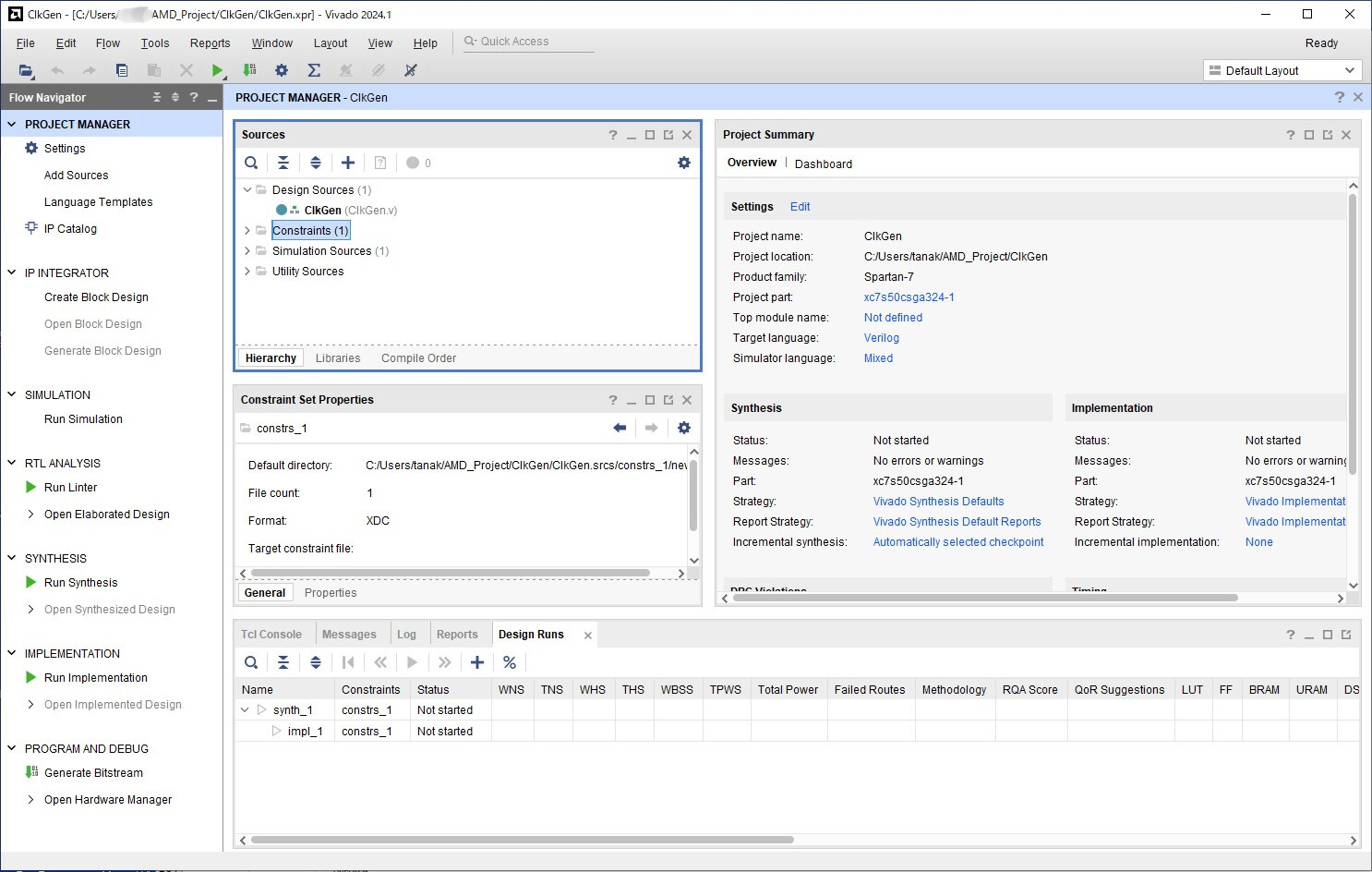

Projectが作成されました。

ここからXDCファイルの変更とソースファイルを作成して行きます。

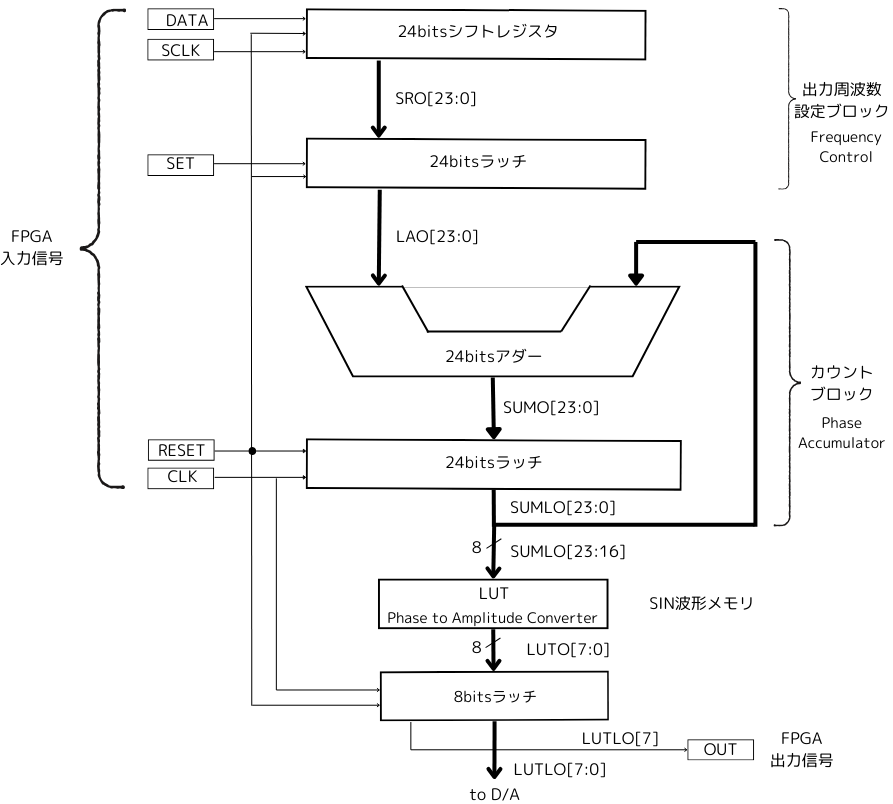

パルス発生回路のブロック図

1.ブロック図

外部CPUからDATA、SCLK、SET信号をシリアルで入力し、パルス周波数を設定します。

LUTは1周期分の出力(正弦)波形を記憶したROMです。

位相加算器の出力の上位8ビットをLUTへ入力します。

位相加算器の出力は出力波形の位相を表し、位相/振幅コンバータを駆動します。

位相/振幅コンバータの出力は出力波形の各入力位相に対する振幅となります。

CLKはシステムクロックであり、このクロック毎に設定した位相が加算されます。

加算量を2倍にすれば、出力周波数も2倍になります。

今回は、CLK = 12[MHz]で駆動します。

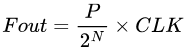

出力周波数を表す式は以下のようになります。

Fout:出力周波数

CLK:システムクロック

N:位相加算器のビット数

P:加算する位相の値

ここでは、N = 24、CLK = 12[MHz]ですので、P = 1ならば

Fout = 0.715[Hz]

となり、Pを増加する毎に、0.715[Hz]ずつ増加します。

P = 2^16 = 65536になるとROMのアドレス入力がシステムクロックCLK毎に

増加します。つまり、ROM1周期を出力する時間は、

1 / 12[MHz] × 2^8 = 1 / 46875[s]

であり、周波数は

Fout = 46875[Hz]

となります。P = 1の時のROM1周期を出力する時間は、

1 / 12[MHz] × 2^16 × 2^8 = 1.398101333[s] = 0.715255453[Hz]

であり、周波数は

Fout = 0.715[Hz]

となります。P = 3の時のROM1周期を出力する時間は、

1 / 12[MHz] × ( 2^16 / 3 ) × 2^8 = 0.466033777[s] =2.145767212[Hz]

であり、周波数は

Fout = 2.145767212[Hz]

となります。ROM出力の分解能を2ビットにして、P = 2^22 = 4194304 とすると、

1 / 12[MHz] × ( 2^16 / 2^22 ) × 2^8 = 1 / 3000000[s]

となり、周波数は

Fout = 3.000000[MHz]

となります。これがシステムクロックCLK = 12[MHz]の時の、LUTLO[7]から取り出せる、

最大出力周波数です。dutyは1:1にはなりませんので、dutyを1:1にしたいときは分周します。

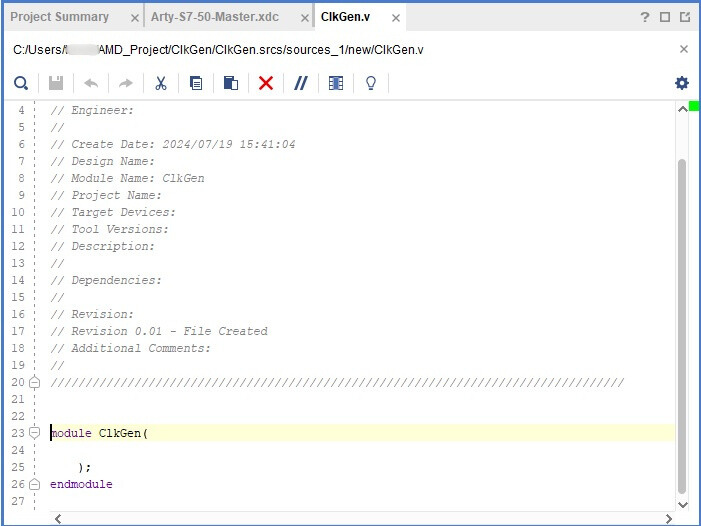

パルス発生回路のVerilog HDL記述

ブロック図の回路をVerilogHDLで記述します。

Vivadoを立ち上げ、プロジェクトClkGenを開きます。

最初に立ち上げたときは何も記入されていませんので、ここから回路を記述します。

入力した結果を示します。

シミュレーション

パルス発生回路のシミュレーションを行います。

1.テストベンチの作成

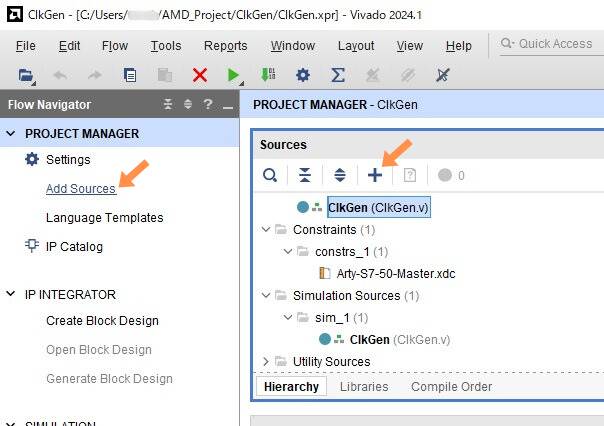

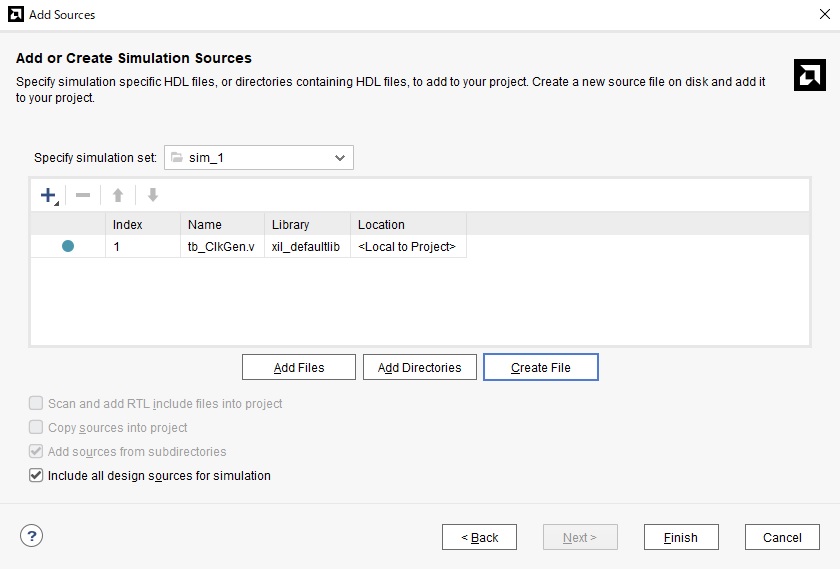

VivadoのProject ManagerでAdd Sourcesを」クリックするか、Sourcesの+をクリックします。

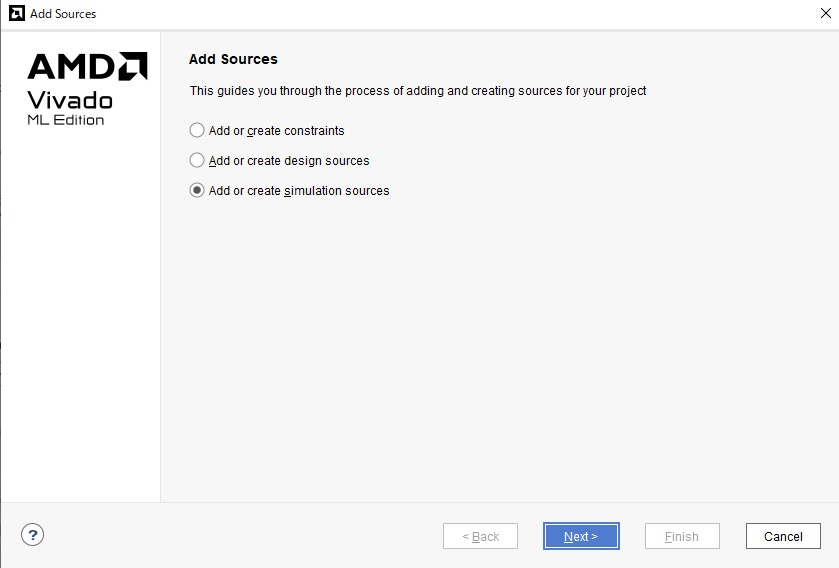

Add or create simulation sourcesを選択してNextをクリック

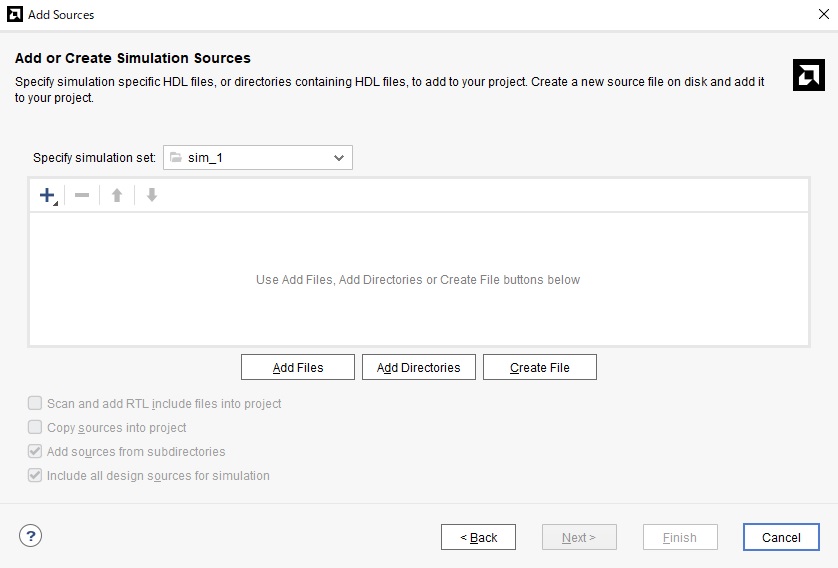

Create Fileをクリック

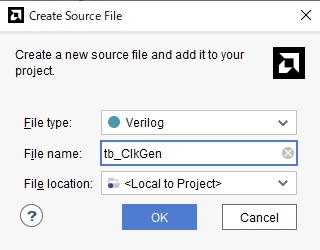

File nameを入力してOKをクリック

Finishをクリック

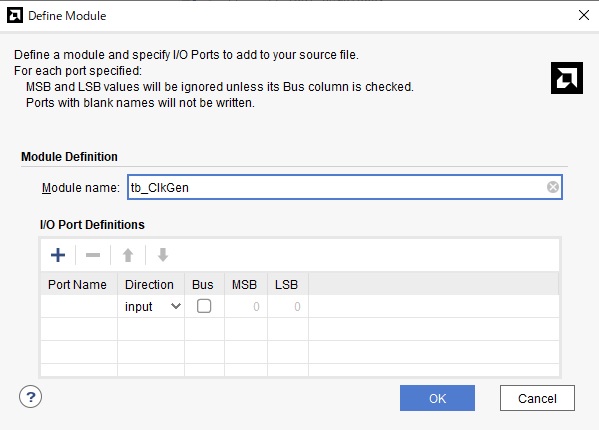

OKをクリック

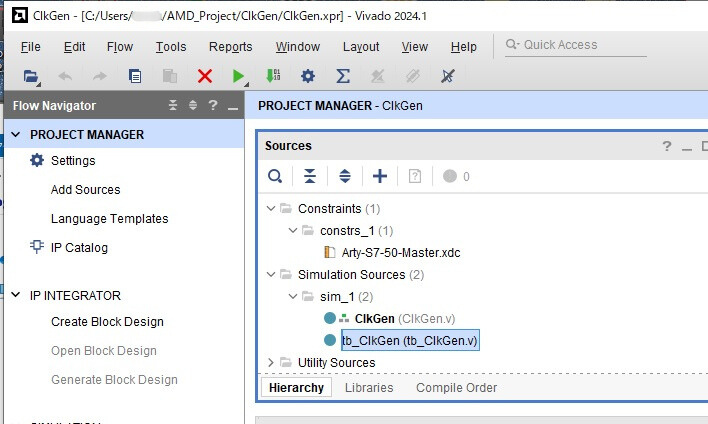

テストベンチがSourcesに追加されました。

ダブルクリックして開きます。

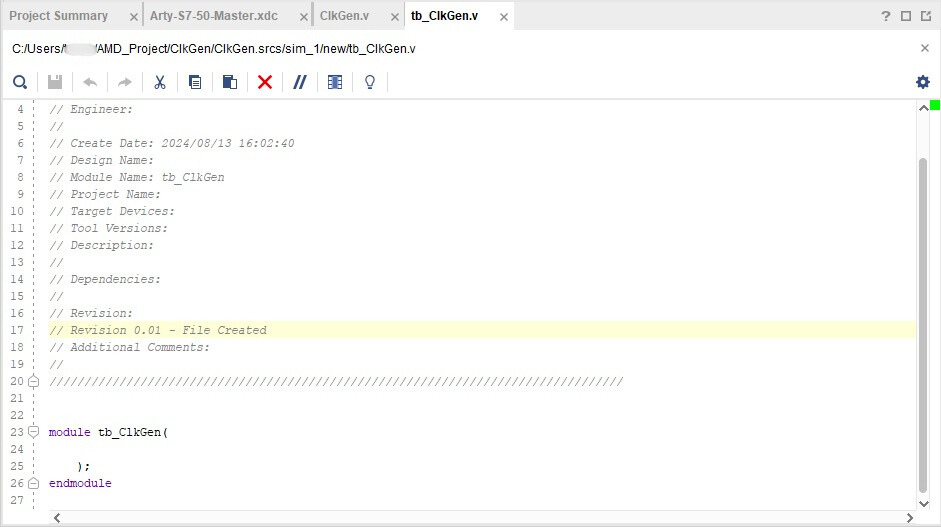

テストベンチを編集します。

編集結果を示します。

VerilogHDLはテストベンチもmodule<モジュール名>から記述します。

ただし、テストベンチには、通常は入出力ポートが無いため入出力ポートの宣言はなく、

ポートリストもありません。検証対象の回路への入力信号を記載します。

具体的には、

(1)検証対象への入力信号の宣言

(2)検証対象(シミュレーション対象モジュール)の呼び出し

(3)検証対象への入力条件の記載。

を行います。

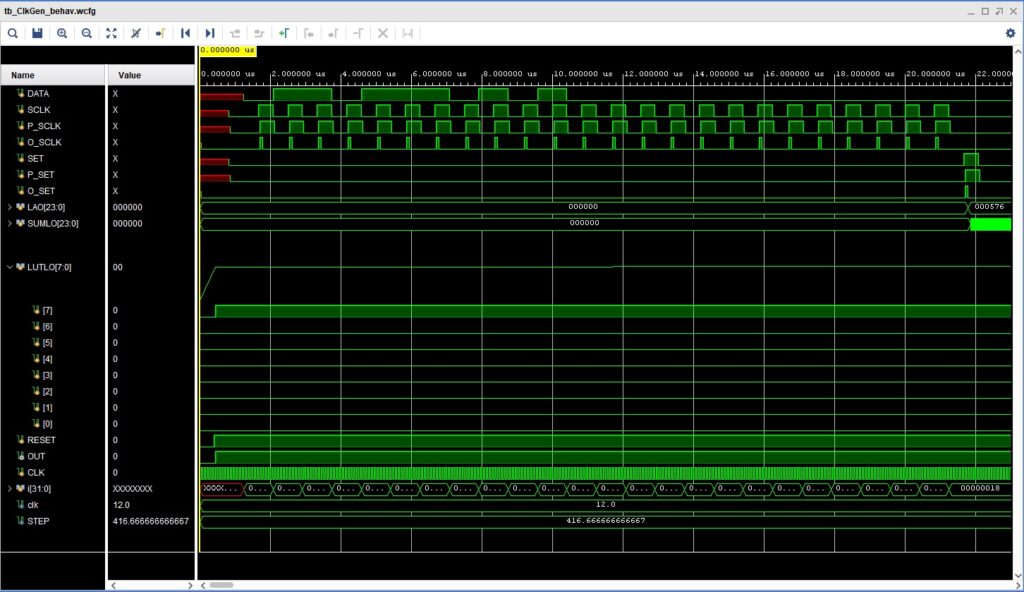

シミュレーション波形を示します。

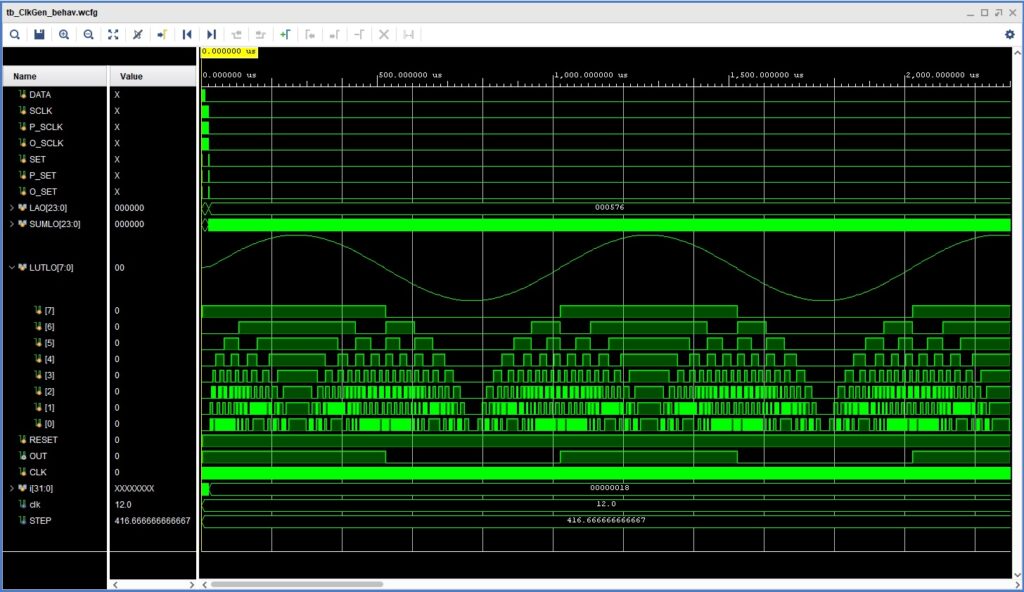

縮小画像を示します。

出力波形をアナログ表示しています。

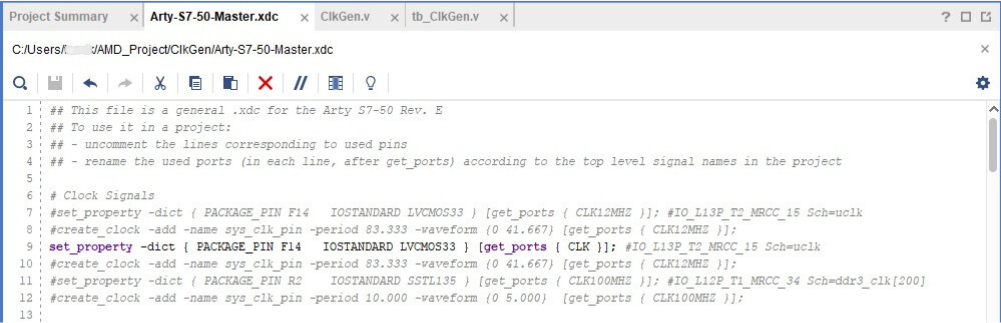

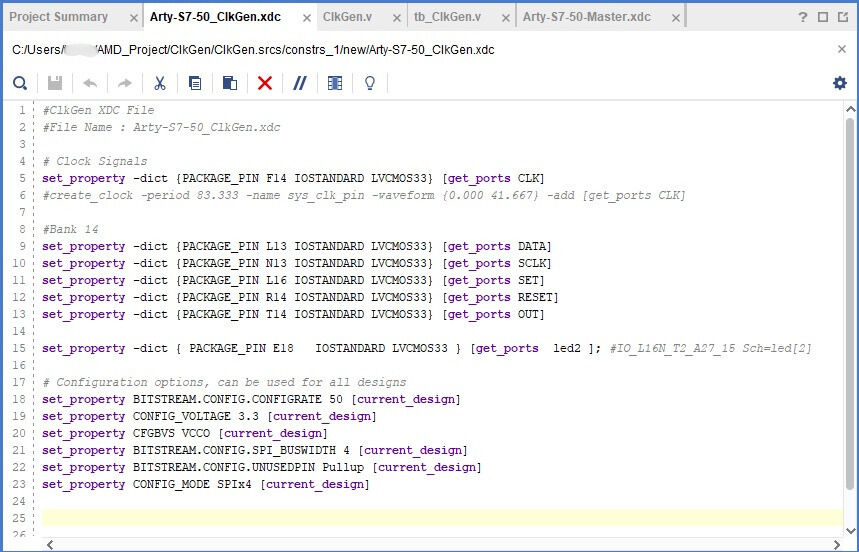

XDCファイルの修正

ArtyS7基板へ書き込むために信号名とI/Oピンを対応させます。

ダウンロードしたXDCファイル(制約ファイル)を修正します。

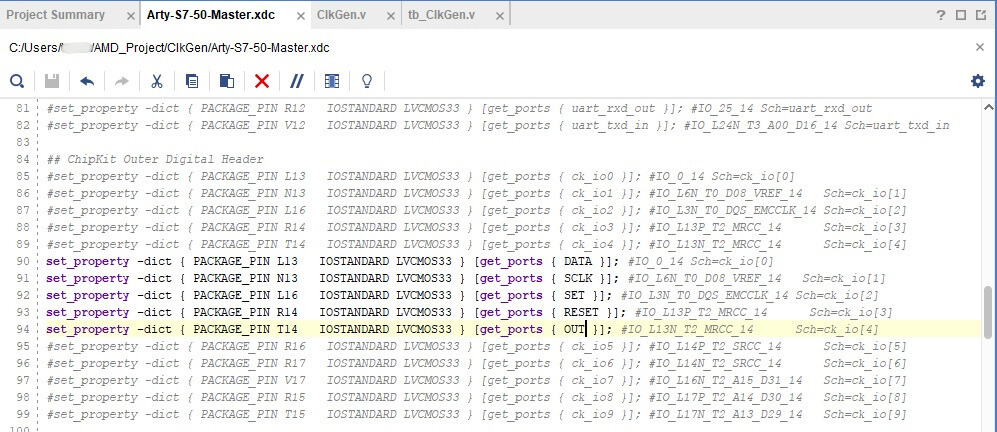

Arty-S7-50-Master.xdcファイルの使用するピンのみコメントアウトを削除します。

(1)CLK12MHz部分のコメントアウトを削除してCLK12MHzをCLKに変更します。

(2)DATA , SCLK, SET, RESET, OUTをそれぞれck_io0, ck_io1, ck_io2, ck_io3, ck_io4

に割り当てます。ARTY S7基板上では、J5コネクタの1,3,5,7,9ピンです。

(3)コメントになっている部分を消してまとめると以下のようになります。

ビットストリームファイルの生成

ビットストリームを生成するためには、Vivado画面左側のFlow Navigatorで

Run Synthesis :xdcファイルの制約と、HDLの回路記述から回路を合成します。

↓

Run Implementation:回路の最適化、レイアウトそして配線を行います。

↓

Generate Bitstream:ビットストリームファイル[*.bit]を生成します。

と進みます。

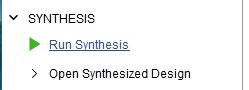

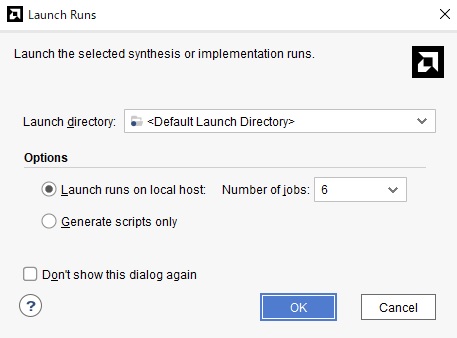

(1)合成(Run Synthesis)

Run Synthesis をクリックします。

OKをクリックします。

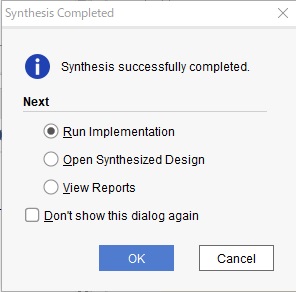

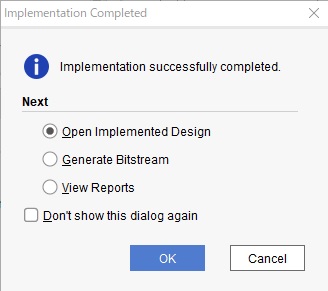

(2)配置配線(Run Implementation)

合成完了の表示が出たら、Run Implementation を選択してOKをクリックします。

配置配線が終了したら、デザインを開くため、OKをクリックします。

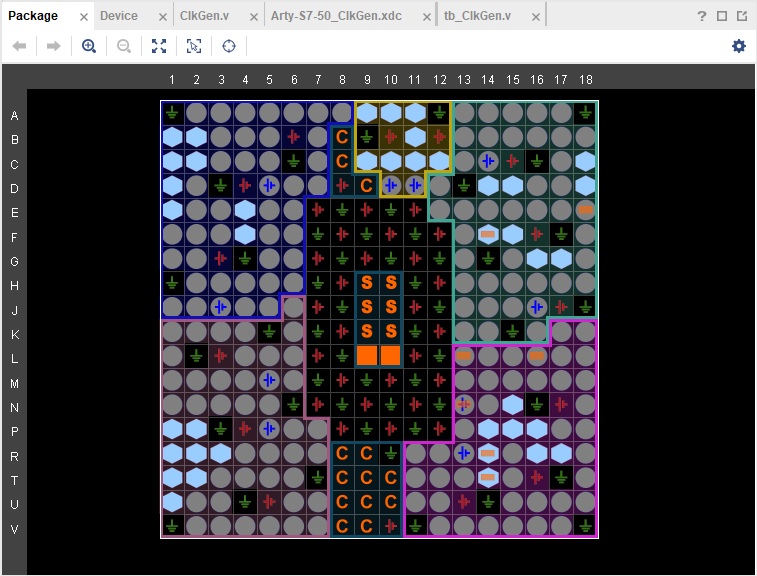

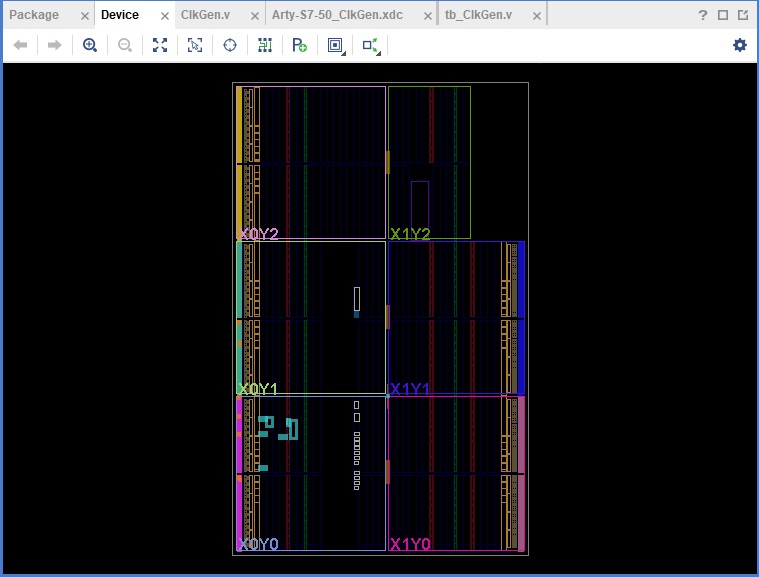

OKをクリックしてPackageとDeviceを表示します。

Package

Device

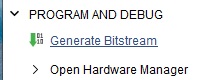

(3)ビットストリームファイル生成

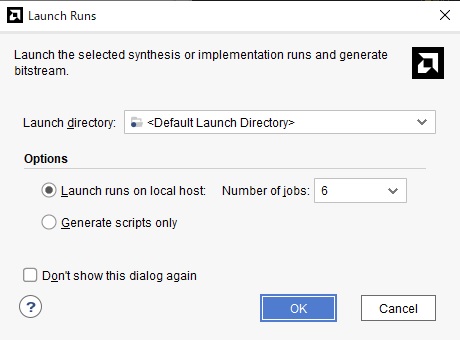

Generate Bitstream をクリック

OKをクリックします。

ボードをPCに接続します。

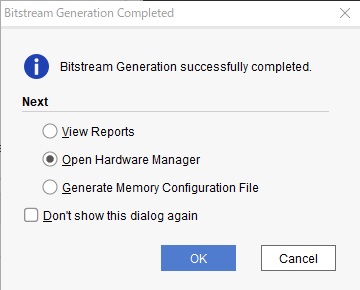

Open Hardware Managerを選択してOKをクリックします。

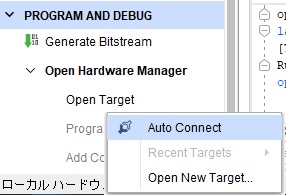

Open Targetをクリックします。

Auto Connectをクリックします。

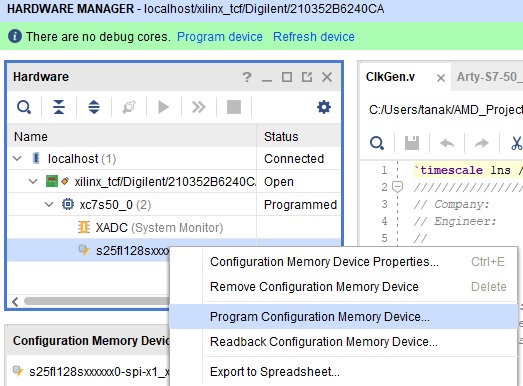

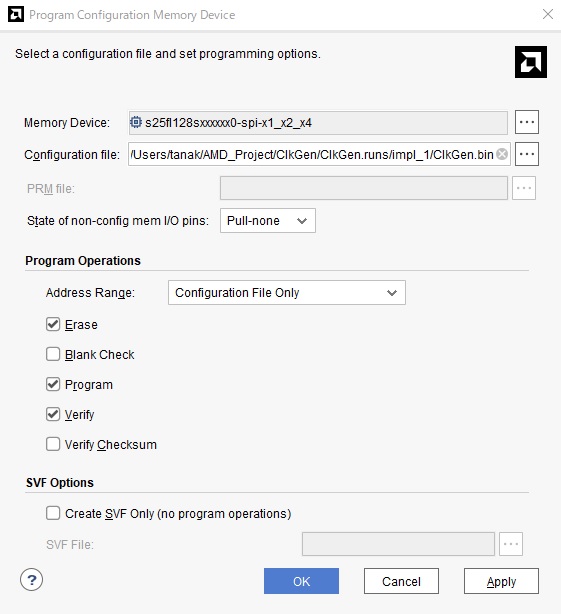

Bit StreamファイルをプログラムするFlashMemoryを右クリックして

Program Configuration Memory Deviceをクリックします。

以下の画面でOKをクリックします。

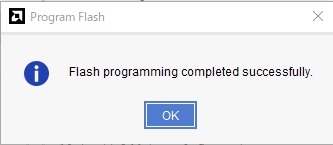

2段階(Step1、Step2)の書込みが終了すると、以下のようになります。

OKをクリックします。

JP1をショートして電源を再投入すれば、FLASHメモリからFPGAへ書き込みが行われます。

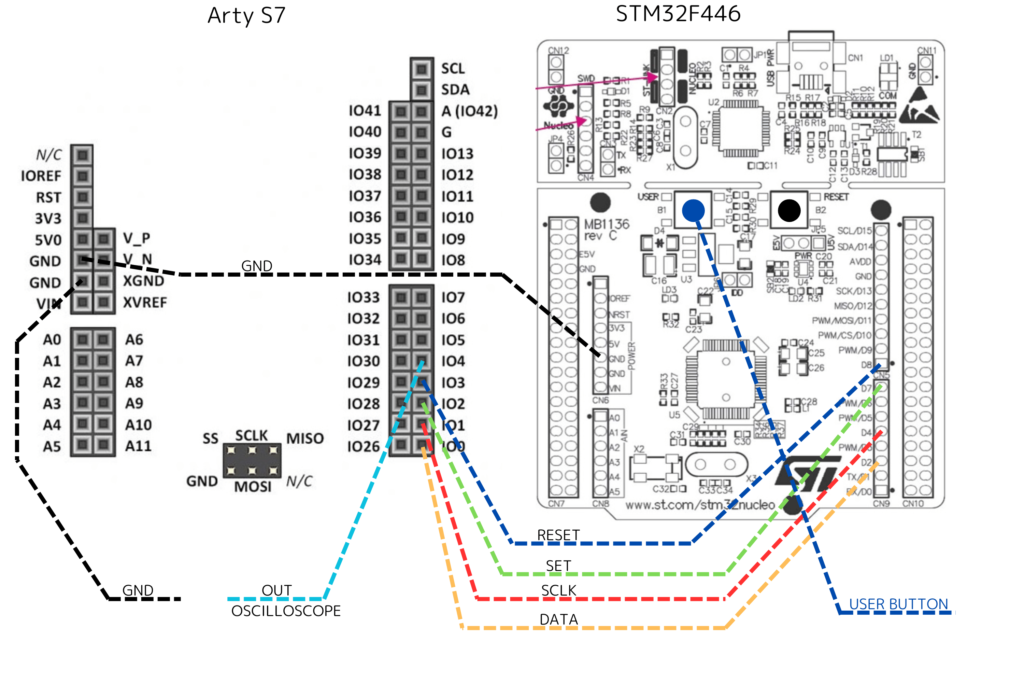

次は外部から周波数を指定するために、STM32マイコンボードを接続します。

STM32マイコンボードから周波数を設定

外部から周波数を設定できるように、マイコンボードを接続します。

ここではSTM32F446NUCLEOボードを以下のように接続し、シミュレーションと同じ

様に、外部よりDATA、SCLK、SET、RESETの各信号を入力します。

STM32のプログラムは別途STM32の項で記載します。

ここでは、プログラムされている前提で説明します。

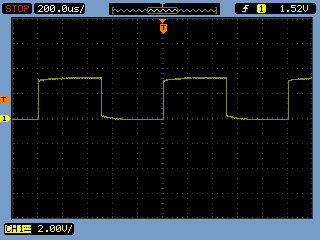

上記のように接続し、Arty S7、STM32の順にUSB接続(電源投入)すると、OUT端子

に初期値の1[KHz]のパルスが出力されます。

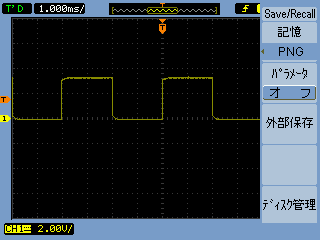

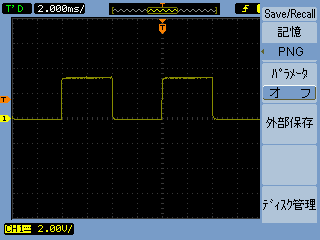

STM32のUSERボタン(青色)を押す度に周波数が1/2になり、一番低くなると次は

1[KHz]に戻ります。これを繰り返します。

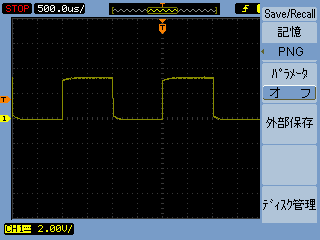

出力波形:1[KHz]

出力波形:500[Hz]

出力波形:250[Hz]

出力波形:125[Hz]

以上で完成です。

Vivadoが出力するエラー

ClkGen.vでは周波数を設定するデータをシリアル入力後に、レジスタにラッチしています。

シリアル入力はSCLK信号、ラッチはSET信号を使用しています。

システムクロックのCLKを使わず、SCLKやSET信号をalways文で以下のように記述すると

always @(posedge SCLK or negedge RESET) begin・・・

や

always @(posedge SET or negedge RESET) begin・・・

です。

以下のようなエラーが出ます。

Implementation faild

これは、

IOピンとBUFG間の配線が不適切なためです。.xdcファイルで

CLOCK_DEDICATED_ROUTE制約を使用すると、Warningに降格できます。

具体的には、ClkGen.xdcファイルに以下の2行を追記します。

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets SCLK_IBUF]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets SET_IBUF]

しかし、この方法は推奨されていません。

今回のClkGen.vのように、SCLKとSETパルスの立ち上がりを捉えて、CLKの1パルス分

のパルスを作成し、このパルスのHighの条件でシフトしたりラッチしたりするようにします。

このようにすればエラーもワーニングも出ません。

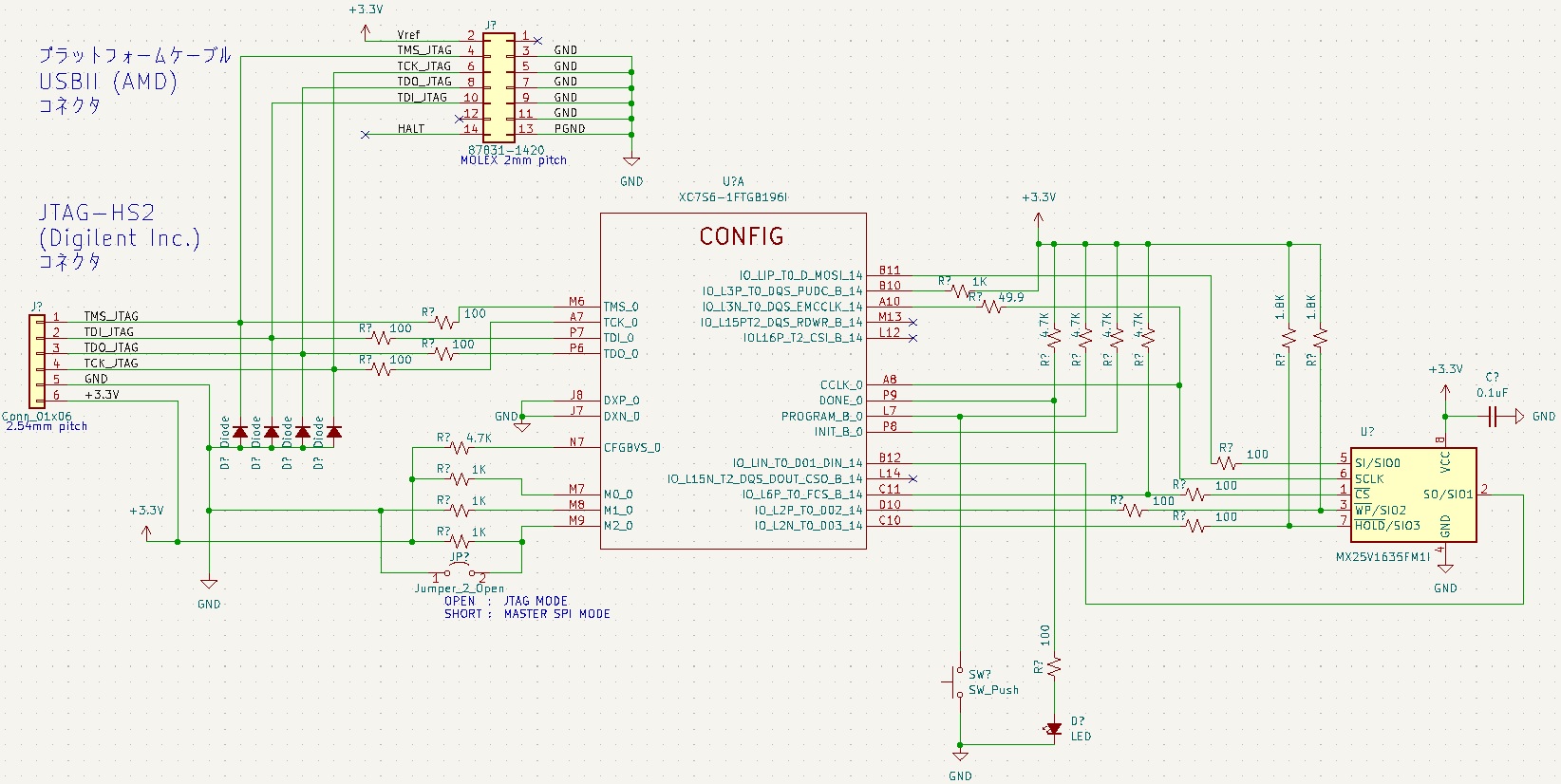

書込回路

Spartan7のCONFIG周辺回路の例を示します。

最小容量のXC7S6を使用した回路での書込み回路で、プラットフォームケーブルUSBII

(AMD)またはJTAG-HS2(Digilent)を接続してFPGA、FLASHのコンフィグレーションを

行います。

続きを読む: FPGAの使い方