Vivadoで作成したProject 「ClkGen」にPLL(MMCM)のIPを組み込みます。

「FPGAの使い方」ではシステムクロックの12MHzを使用して発振回路を作成しました。

12MHzでは、1KHzを出力するために設定するパラメータが1398でした。

直感的にわかりにくいため、パラメータを1000と入力して、1KHzを出力できるように

したいと思います。

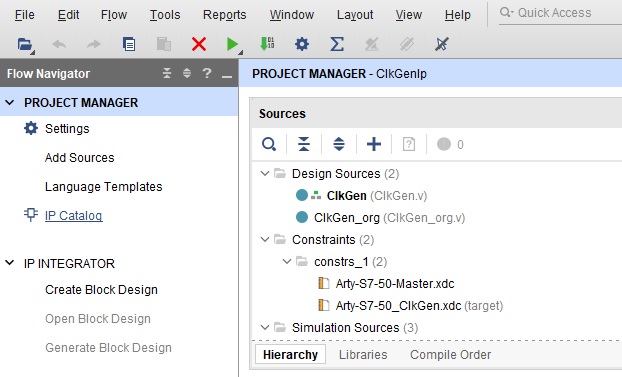

IPカタログからClocking Wizardを選ぶ

ClkGenをClkGenIpという名前でコピーし、起動します。

VivadoのFlow NavigatorのIP Catalogをクリックし、IP Catalogの検索窓で、clocking

と入力し、Clocking Wizardを選択します。

Clocking Wizardをダブルクリックします。

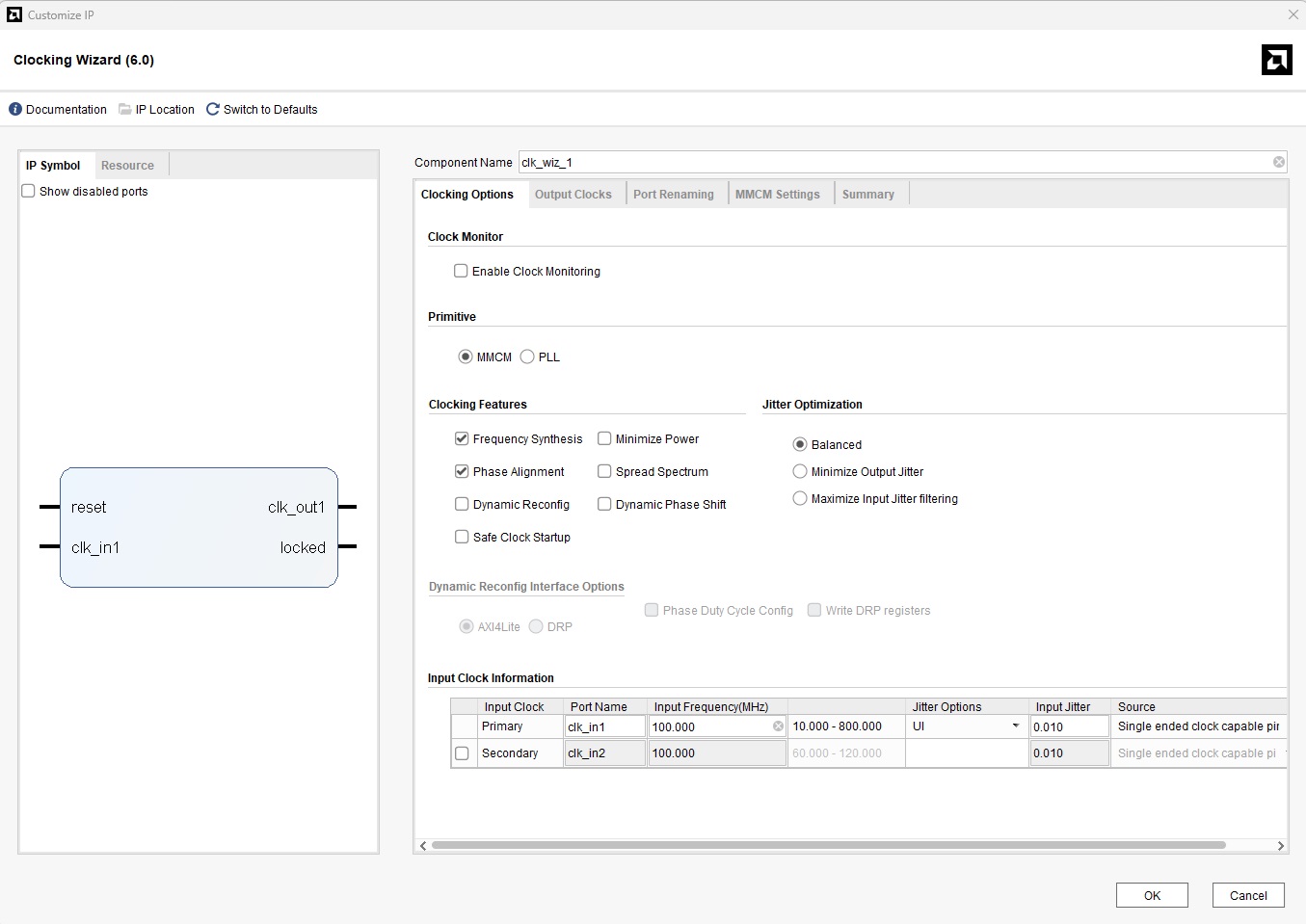

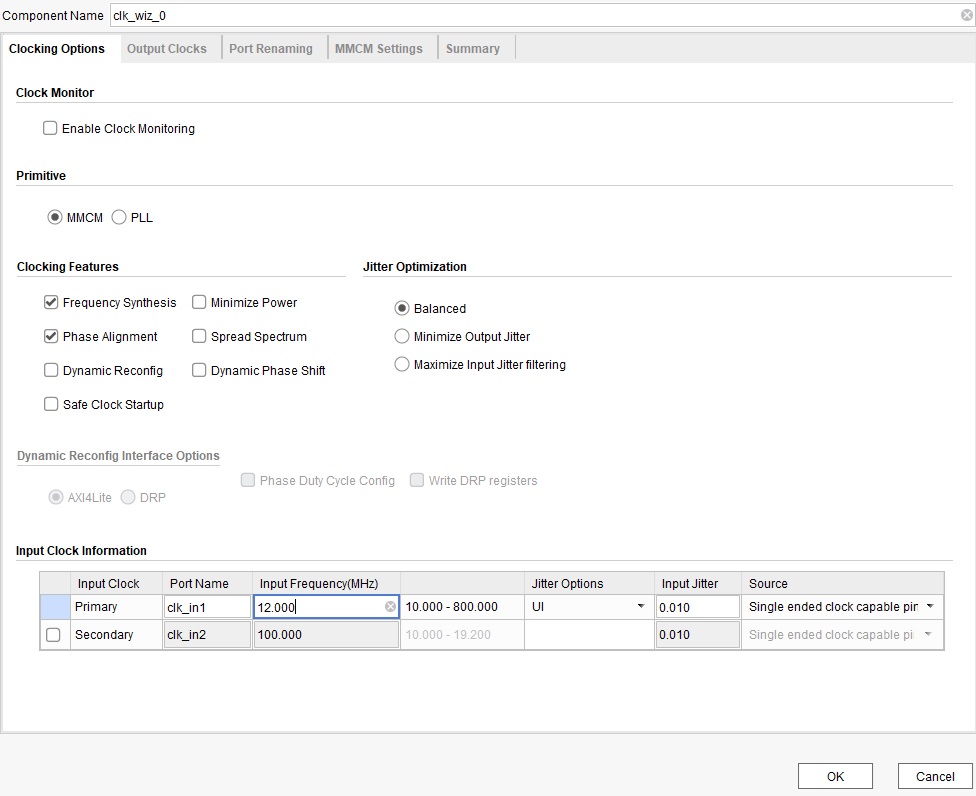

MMCMで入力クロックを12.000[MHz]に設定します。

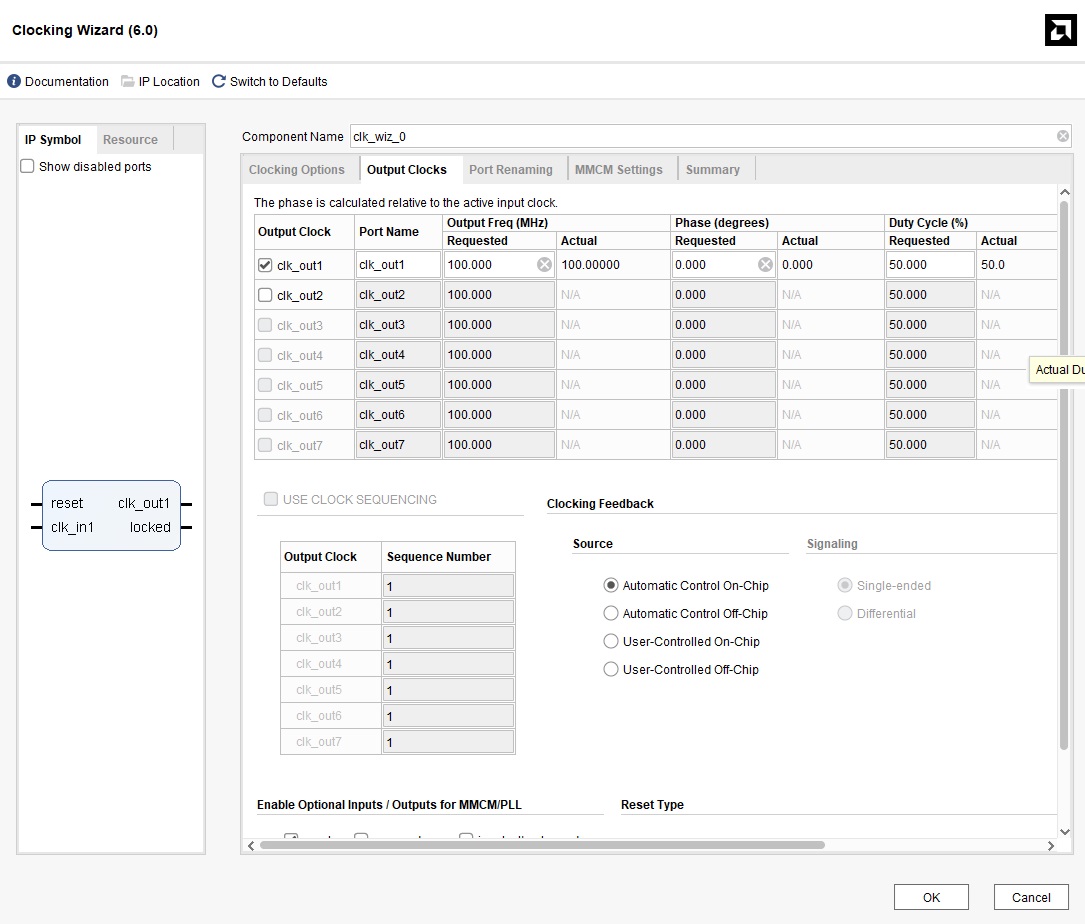

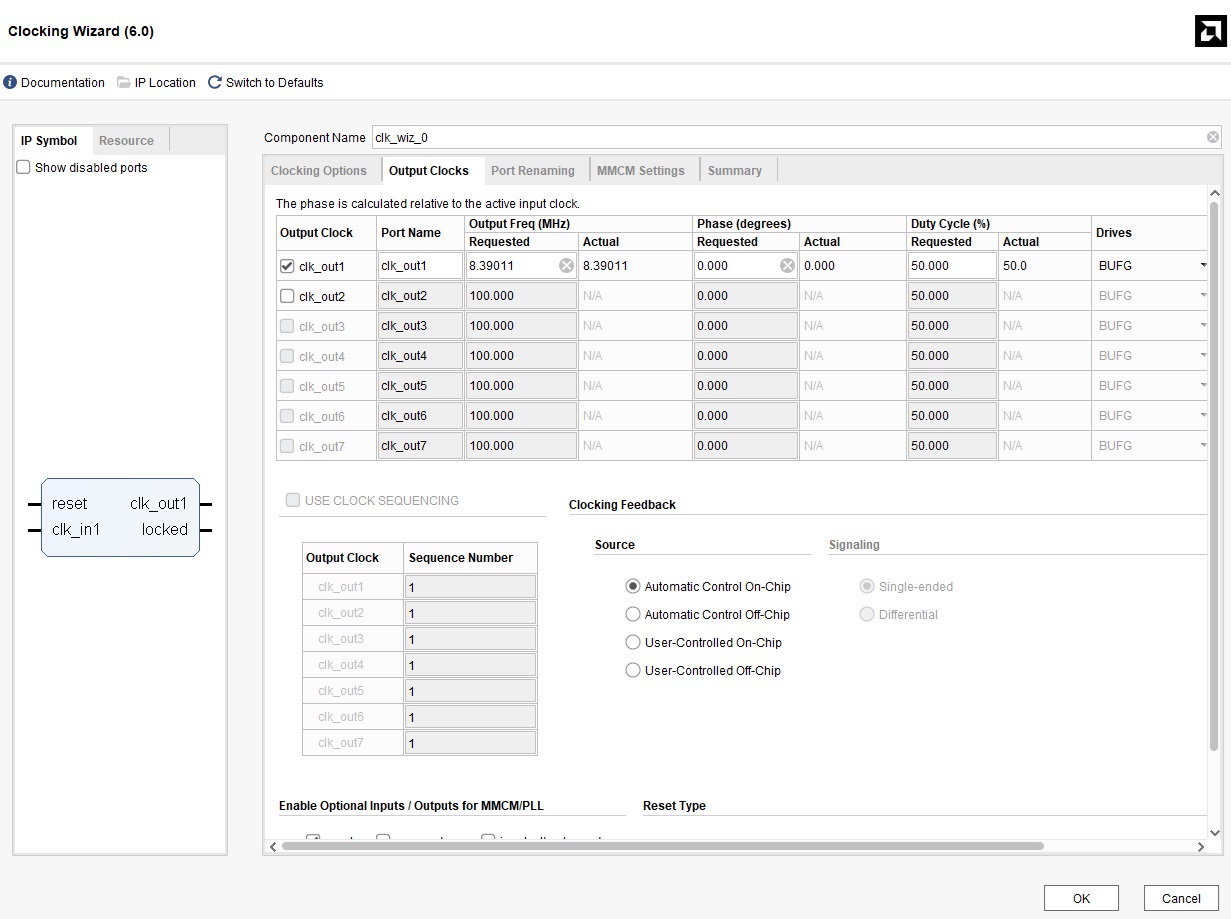

Output Clocksタブを開きます。

出力周波数を8.39011[MHz]に設定します。これは8.388608[MHz]に一番近く、設定可能な

周波数です。

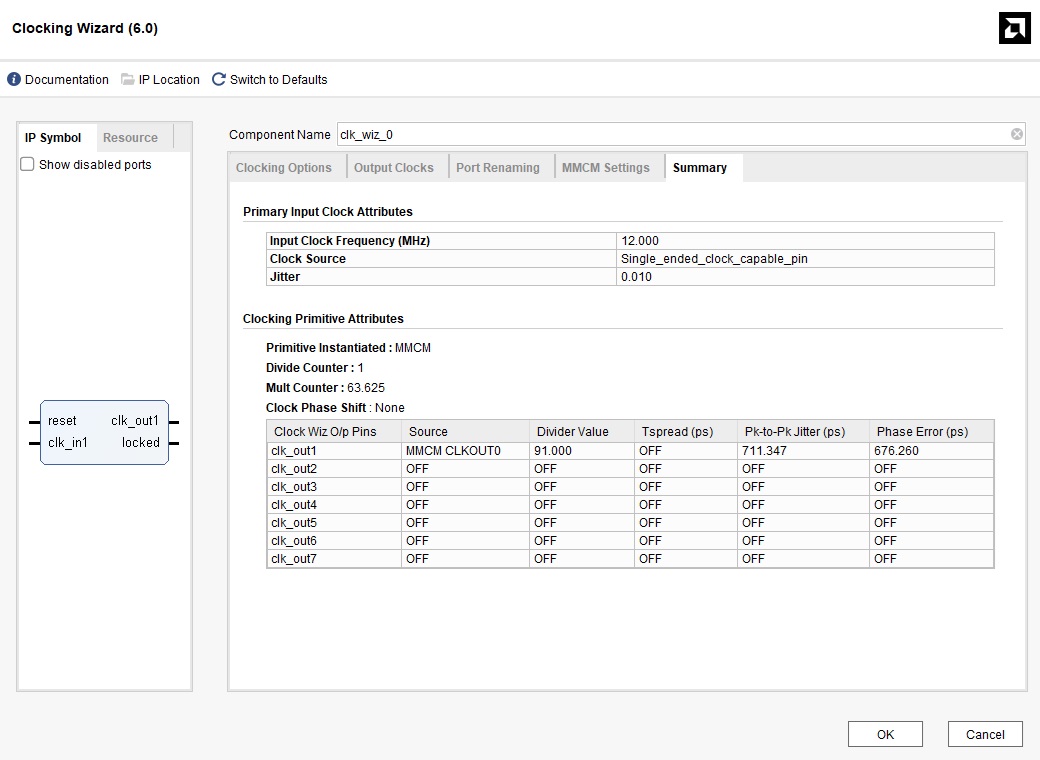

Summaryタブを開きます。

clk_out1は、入力クロックを63.625倍し91で割った周波数に設定されています。

(clk_out = 12 * 63.625 / 91 = 8.39011)

OKボタンをクリックしてClocking Wizardを終了します。

IPをプロジェクトに組込む

IPコアが生成できましたので、プロジェクトのデザインに組込みます。

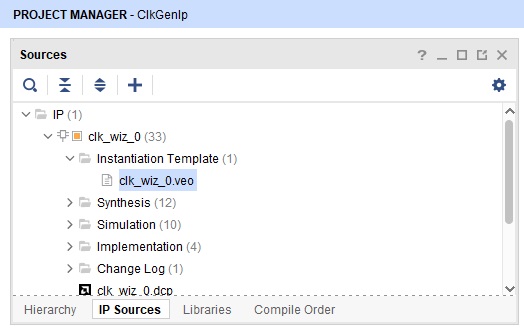

PROJECT MANAGERのSourcesペインでIP Source選択し、デザインに組込むための

テンプレートファイルclk_wiz_0.veoをダブルクリックして開きます。

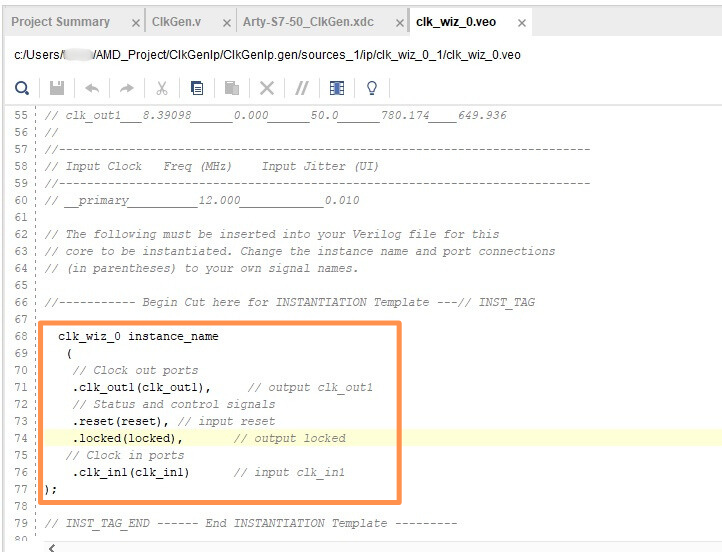

開いたファイルにの以下の部分を、ソースファイルClkGen.vにコピーして貼り付け修正します。

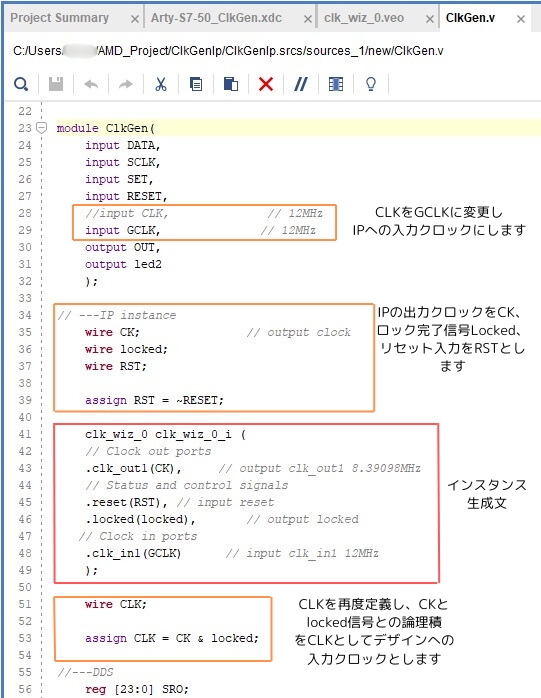

ClkGen.vを以下のように追加、変更します。

テストベンチを変更

テストベンチを以下のように変更します。

95行目をWrFreq(1398)からWrFreq(1000*2)に変更しています。 これはシステムクロックが

12[MHz]から8.39098[MHz](4.19549[MHz] * 2)に変更したためです。4.19549[MHz]であれば

WrFreq(1000*2)で1[KHz]が出力されます。

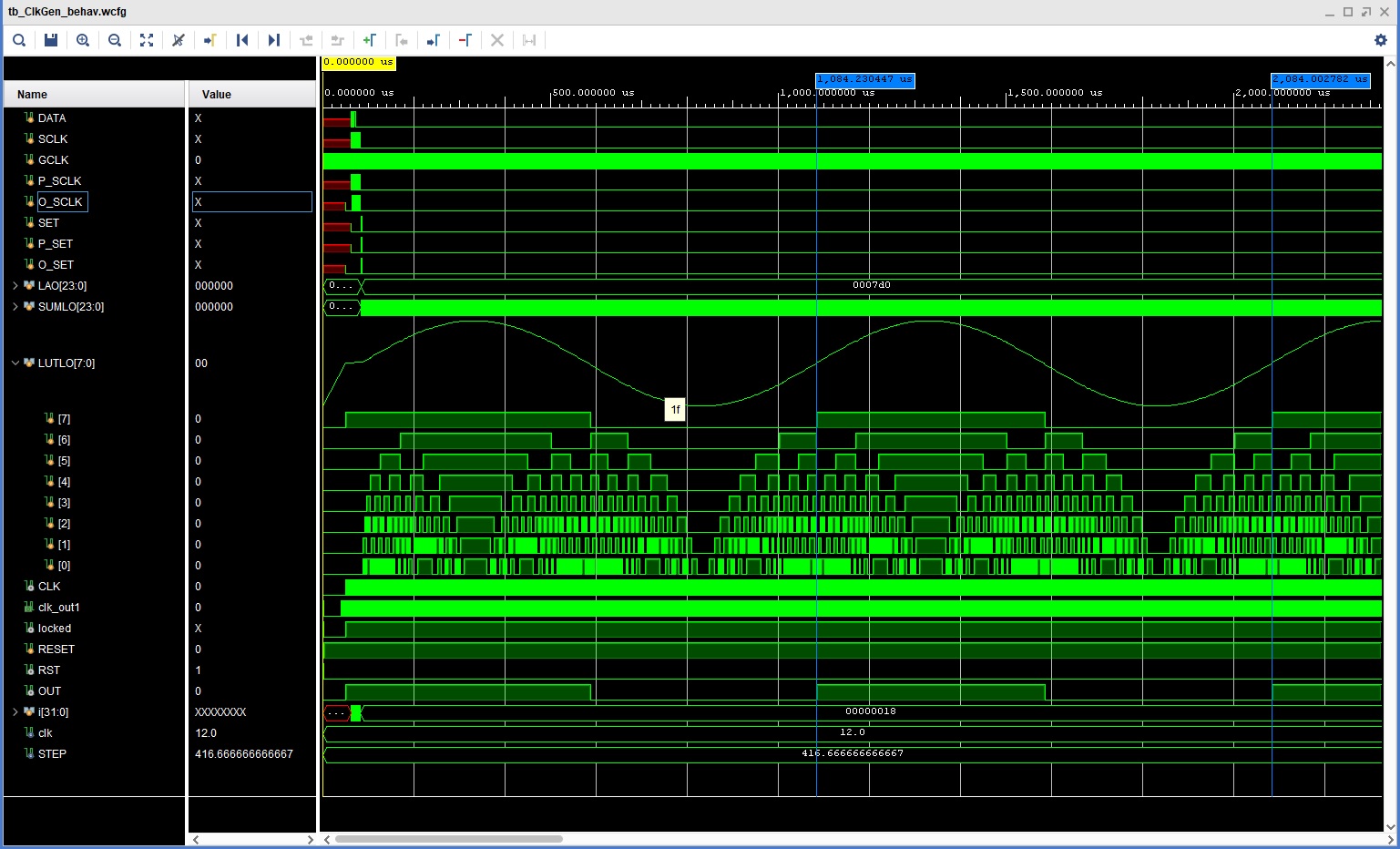

シミュレーション

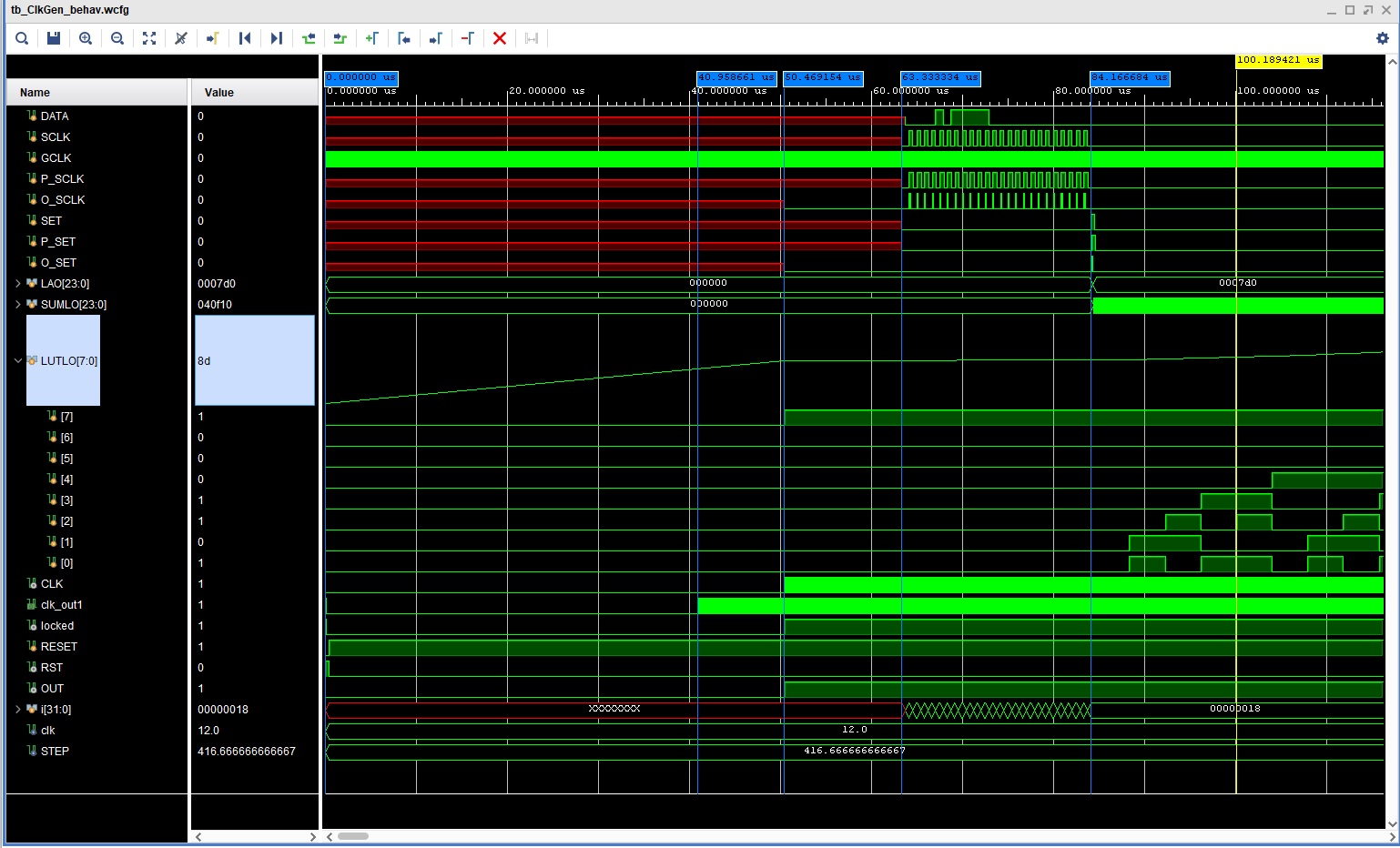

このテストベンチでシミュレーションを行いました。

先頭部分

全体

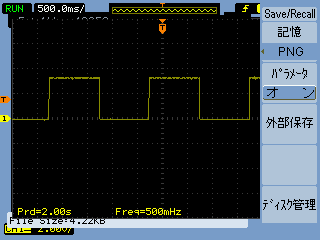

OUT信号の周期が1[ms](正確には0.99977[ms])で1[KHz]になっているのがわかります。

正確に1[ms]にするためにはCLKを8.388608[MHz]にすれば良いのですが、Clocking Wizardでは

8.39098[MHz]までしか設定できませんで

ビットストリームファイルの生成と基板への書込み

「FPGAの使い方」の要領でビットストリームファイルを作成し、基板のFLASHへ書き込みます。

STM32マイコンボードから周波数を設定

「FPGAの使い方」の要領でSTM32マイコンボードから周波数を設定します。

STM32マイコンボードのプログラムを少し変更しています。

変更内容はSTM32マイコンボードの記事に記載しました。

ここでは結果を示します。

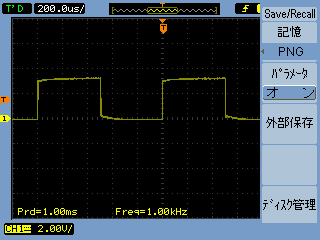

[立ち上げ時]

[USERボタンを1回押した時]

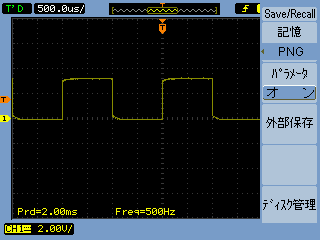

[USERボタンを2回押した時]

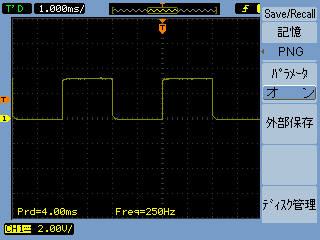

[USERボタンを10回押した時]

11回USERボタンを押すと1[KHz]へ戻ります。